随着集成电路制造技术持续演进,堆叠纳米片环栅场效应晶体管(Stacked Nanosheets GAA FET)在3纳米以下节点将替代传统鳍型晶体管(FinFET),从而进一步推动半导体产业发展。但面对大规模制造的需求,GAA晶体管技术还需突破N型与P型器件工作电流(Ion)严重失配和阈值电压(Vth)调控困难等关键挑战,对纳米片沟道材料以及高 金属栅材料提出了更多技术创新要求。因此,针对GAA晶体管进行器件结构创新已成为未来逻辑器件工艺研究的重要方向。

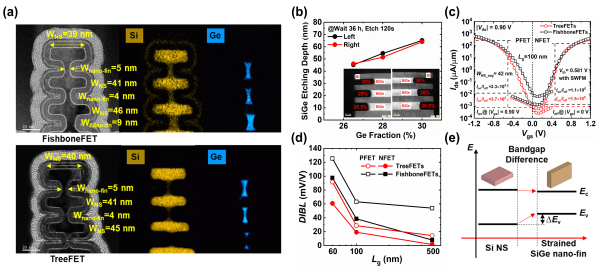

近日,微电子所先导中心殷华湘研究员团队基于主流GAA晶体管的制造工艺,在体硅衬底上通过调整SiGe/Si叠层外延中底部SiGe层的Ge含量,并在后栅沟道中采用纳米级高选择比SiGe层刻蚀技术,首次设计并制备出沟道结构类似鱼骨状的GAA器件(FishboneFET)。由于在传统堆叠Si纳米片间引入额外的应变SiGe nano-fin结构,在相同的平面投影面积下大幅增加了GAA器件中的沟道导电面积并提升了P型器件的驱动性能。相比同类型的树型(Tree-like)GAA器件(TreeFET),所设计的FishboneFET进一步改善了N型与P型器件的电学性能失配问题,并利用单一功函数金属栅材料实现了面向CMOS器件的阈值调控,解决了FishboneFET晶体管在CMOS集成中的关键挑战。基于上述创新技术,研究团队在国际上首次研制成功兼容主流GAA器件工艺的CMOS FishboneFET和TreeFET器件,获得高的N/PFET器件电流开关比,在单一功函数金属栅下获得更为平衡的N型与P型GAA器件驱动性能匹配,并发现N型TreeFET和FishboneFET在抑制短沟道器件的漏致势垒降低(DIBL)效应上更具优势,且TreeFET较FishboneFET具有更低的DIBL效应。研究团队提出了应变SiGe nano-fin中的价带补偿理论,成功解释了新结构中的特殊电学效应,为新型GAA晶体管导入高性能CMOS集成电路应用建立了关键技术路径。

该成果近日以“Investigation of Fabricated CMOS FishboneFETs and TreeFETs With Strained SiGe Nano-Fins on Bulk-Si Substrate”为题发表在国际微电子器件领域的高水平期刊《电气和电子工程师协会电子器件快报》上(IEEE Electron Device Letters, Vol. 44, No. 9, 1396 (2023), DOI: 10.1109/LED.2023.3294545),并成为EDL主编重点推荐和评委“亮点文章”(Editors’ Picks),微电子所先导中心博士生曹磊为该文章第一作者。殷华湘研究员、张青竹青年研究员为该文通讯作者。该项研究得到中国科学院战略性先导专项(A类)、国家自然科学基金委等项目的支持。

(原文链接:https://ieeexplore.ieee.org/document/10180010)

图(a)新型FishboneFET与TreeFET结构的TEM结果,(b)堆叠SiGe/Si层中SiGe材料双端刻蚀深度随Ge含量变化趋势,(c)100 nm栅长器件的Ids-Vgs特性@Vdsat= 0.9 V,(d)器件的DIBL效应随栅长变化关系,(e)Si NS和应变SiGe nano-fin的能带示意图

综合新闻