垂直沟道纳米器件因其对栅长限制小、布线灵活及便于3D一体集成等天然优势,在1纳米逻辑器件/10纳米DRAM存储器及以下技术代的集成电路先进制造技术方面具有巨大应用潜力。

要实现垂直沟道纳米晶体管的大规模制造,须对其沟道尺寸和栅极长度进行精准控制。对于高性能垂直单晶沟道纳米晶体管,现阶段控制沟道尺寸最好方法是采用先进光刻和刻蚀技术,但该技术控制精度有限,导致器件性能波动过大,不能满足集成电路大规模先进制造的要求。

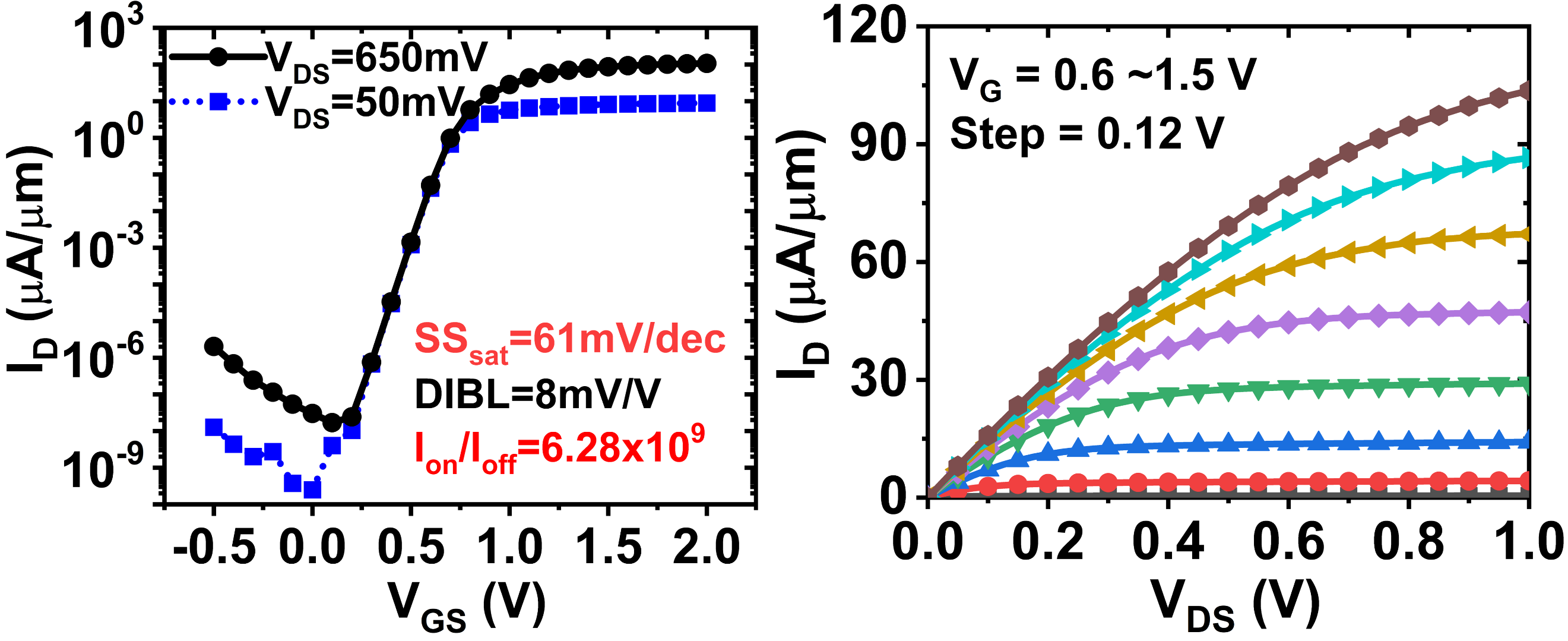

微电子所集成电路先导工艺研发中心朱慧珑研究员团队,在实现对栅极长度和位置精准控制的基础上,提出并研发出了一种C型单晶纳米片沟道的新型垂直器件(VCNFET)以及与CMOS技术相兼容的“双面处理新工艺”,其突出优势是沟道厚度及栅长/位置均由外延层薄膜厚度定义并可实现纳米级控制,为大规模制造高性能器件奠定了坚实基础,研制出的硅基器件亚阈值摆幅(SS)以及漏致势垒降低(DIBL)分别为61mV/dec和8mV/V,电流开关比高达6.28x109,电学性能优异。

近日,该研究成果以“Vertical C-Shaped-Channel Nanosheet FETs Featured with Precise Control of both Channel-Thickness and Gate-Length”为题发表在电子器件领域著名期刊IEEE Electron Device Letters(DOI: 10.1109/LED.2022.3187006)上,先导中心博士生肖忠睿为该文第一作者,朱慧珑研究员为通讯作者。

该研究得到科技部、中科院和北京超弦存储器研究院的项目资助。

论文链接:https://ieeexplore.ieee.org/document/9810318

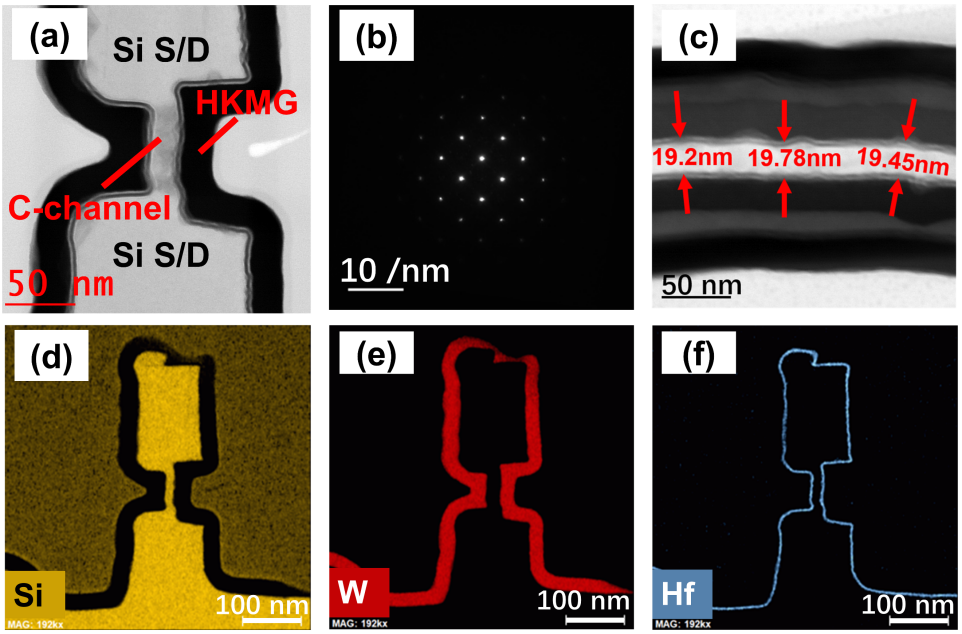

图1 (a) 垂直纳米片器件的TEM截面图 (b) 器件沟道中心位置的纳米束衍射花样 (c) 外延硅沟道的TEM俯视图 (d)-(f) 器件截面的EDS能谱图

图2 垂直纳米片器件的转移输出特性曲线

| 相关新闻: |

| 微电子所在超低功耗集成电路与人工智能领域取得新进展 |

| 微电子所在三维深度储备池计算领域取得进展 |

| 微电子所在新型垂直互补场效应晶体管(CFET)结构设计与仿真研究方面取得进展 |

综合新闻