NOR闪存以速度快、可靠性高和使用寿命长等优势,在人工智能、汽车电子和工业领域中发挥着不可替代的作用。目前普遍使用的平面NOR闪存在50纳米以下技术代的尺寸微缩遇到瓶颈,难以进一步提升集成密度、优化器件性能和降低制造成本。为突破上述瓶颈,研究人员提出了多种基于多晶硅沟道的三维NOR(3D NOR)器件,但多晶硅沟道迁移率低、读取速度慢,影响了NOR器件整体性能。

近日,微电子所集成电路先导工艺研发中心朱慧珑研究员团队研发制备出一种高性能单晶硅沟道3D NOR储存器。遵循知识产权保护优先的原则,自2021年起,朱慧珑在器件结构、集成工艺和电路架构等方面先后提出了多个解决方案并提交了相应专利申请。该团队使用研发的垂直晶体管新工艺制备出单晶硅沟道3D NOR三维阵列,其上下叠置的晶体管既具单晶硅沟道的高性能优势,又有三维一体集成的制造成本低的优点,可在获得同等或优于单晶硅沟道平面NOR闪存器件性能的同时,无需升级光刻机也可大幅提高存储器集成密度、增加存储容量。团队研制的3x3x2三维NOR闪存阵列实现了正常读写和擦除,达到了读电流以及编程、擦除速度与二维NOR闪存器件相当的目标,且新制程与主流硅基工艺兼容,便于应用。

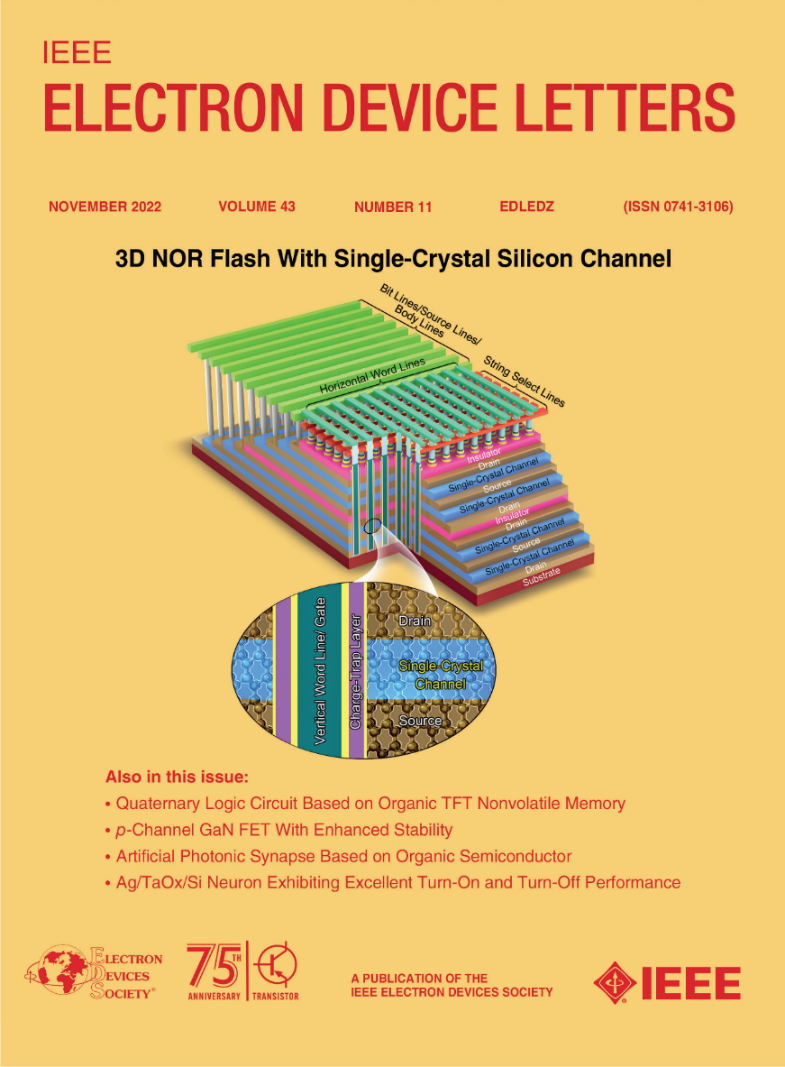

相关成果作为封面和“编辑特选”(Editors Picks)文章,以题为“A Novel 3D NOR Flash with Single-Crystal Silicon Channel: Devices, Integration, and Architecture”发表在国际微电子顶刊《IEEE Electron Device Letters》上。微电子所博士研究生黄伟兴是第一作者,朱慧珑为通讯作者,这也是朱慧珑研究团队的垂直纳米器件相关成果再次入选“编辑特选”文章。

该研究部分得到中国科学院自主部署项目(Y7YC01X001)的资助。

论文链接:https://ieeexplore.ieee.org/document/9906527

图1.刊登在《Electron Device Letters》封面上的单晶硅3D NOR电路架构(上)及垂直沟道晶体管结构(下)

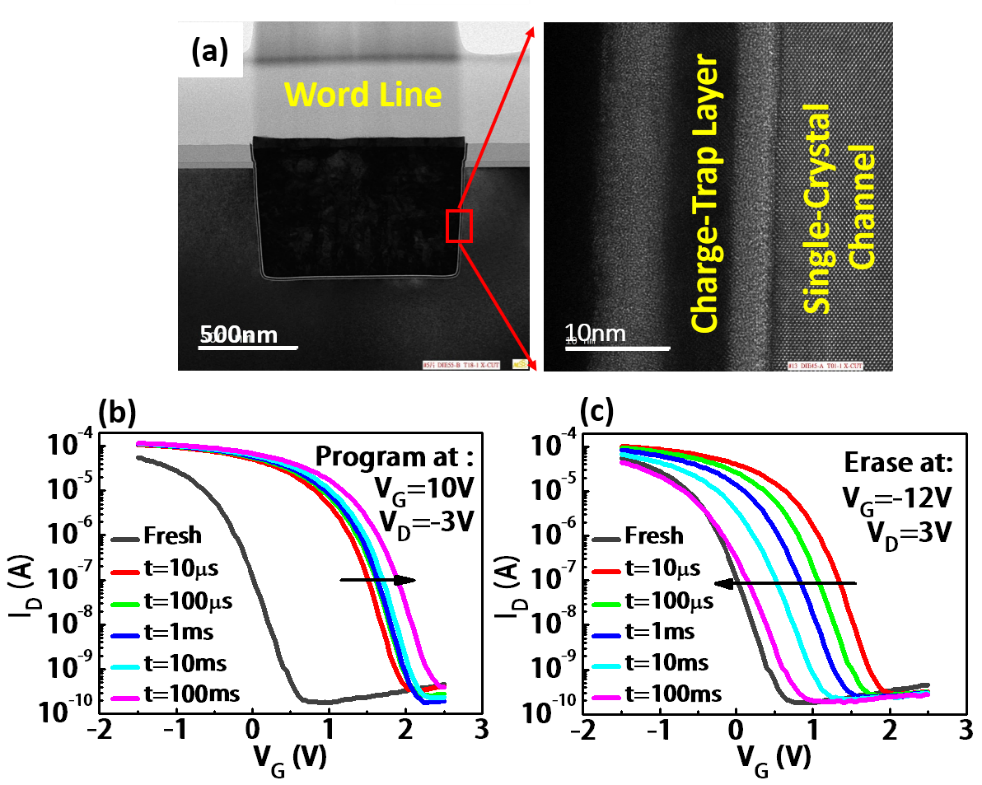

图2. 单晶硅沟道3D NOR器件及电性实验结果:(a)器件TEM截图(左)及沟道局部放大图(右),(b)编程特性和(c)擦除特性

| 相关新闻: |

| 中科院微电子所与华为海思合作在无外磁场写入的自旋轨道矩磁隧道结器件的研究中取得新进展 |

| 微电子所垂直沟道纳米晶体管研发工作再获重要突破 |

| 微电子所在无外场单级电压控制SOT-MTJ自旋逻辑器件的研究中取得新进展 |

综合新闻