成果展示

微电子所在阻变存储器研究领域取得新突破

日前,微电子所微电子器件与集成技术重点实验室刘明院士团队在阻变存储器(RRAM)三维垂直交叉阵列研究领域取得了突破性进展,提出了自对准高性能自选通阻变存储器结构,为高密度、低成本三维垂直交叉阵列的制备提供了解决方案,以题为“Fully CMOS compatible 3D vertical RRAM with self-aligned self-selective cellenabling sub-5nm scaling”(通讯作者:吕杭炳、刘明)的论文被2016 Symposia on VLSI Technology and Circuits(简称VLSI国际研讨会)接收,第一作者许晓欣在会上进行了口头报告。这是中国科学院首次作为第一作者单位在该国际会议上发表论文。

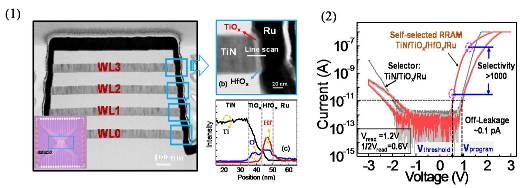

在实现阻变存储器高密度应用方面,垂直结构的交叉阵列具有制备工艺简单,成本低廉等优点。自选通阻变器件是该阵列架构的核心,一般由选通层和阻变层组成。当垂直交叉阵列极限微缩时,层间的漏电会将成为重要的问题。针对这一问题,刘明课题组在国际上首次提出了采用自对准技术构建自选通阻变器阵列架构的方法,有效消除了阵列中的层间漏电流,使垂直阻变存储阵列的微缩能力达到5nm以下。研制成功的自对准自选通阻变器件同时也表现出优良的阻变性能:漏电流<0.1pA,非线性比>1000,操作电流<1uA以及很好的保持特性和耐久性。

VLSI国际研讨会成立于1987年,是全球先进半导体与系统芯片学术发表盛会,是国际微电子领域的顶级会议,与IEDM和ISSCC并称微电子技术领域的“奥林匹克盛会”。VLSI国际研讨会只接收极具应用前景的创新性研究成果,Intel、IBM等公司的许多核心技术都是在VLSI国际研讨会上首次披露的。

(1)四层3D VRRAM阵列的TEM 图以及4层 8×32 1Kbit阵列光学示意图。垂直阻变器件基于TiN/TiOx/HfOx/Ru结构,具有自对准的选择层。(2)自对准的自选择器件的典型I-V 特性曲线。