物联网与人工智能技术的迅猛发展对边缘节点计算平台的实时数据处理能力与能效提出了更高要求。基于新型存储器的非易失存内计算技术可实现数据的原位存储与计算、将数据搬运带来的功耗与延迟开销最小化,从而大幅提升边缘设备的数据处理能力与效能比。但由于基础单元特性的非理想因素,阵列中的寄生效应以及模数转换电路的硬件开销,非易失存内计算仍面临计算性能与能效方面的限制。

围绕上述关键问题,微电子所刘明院士团队采用跨层次协同设计的方法,提出了高并行与高效能比的新型RRAM存内计算结构。

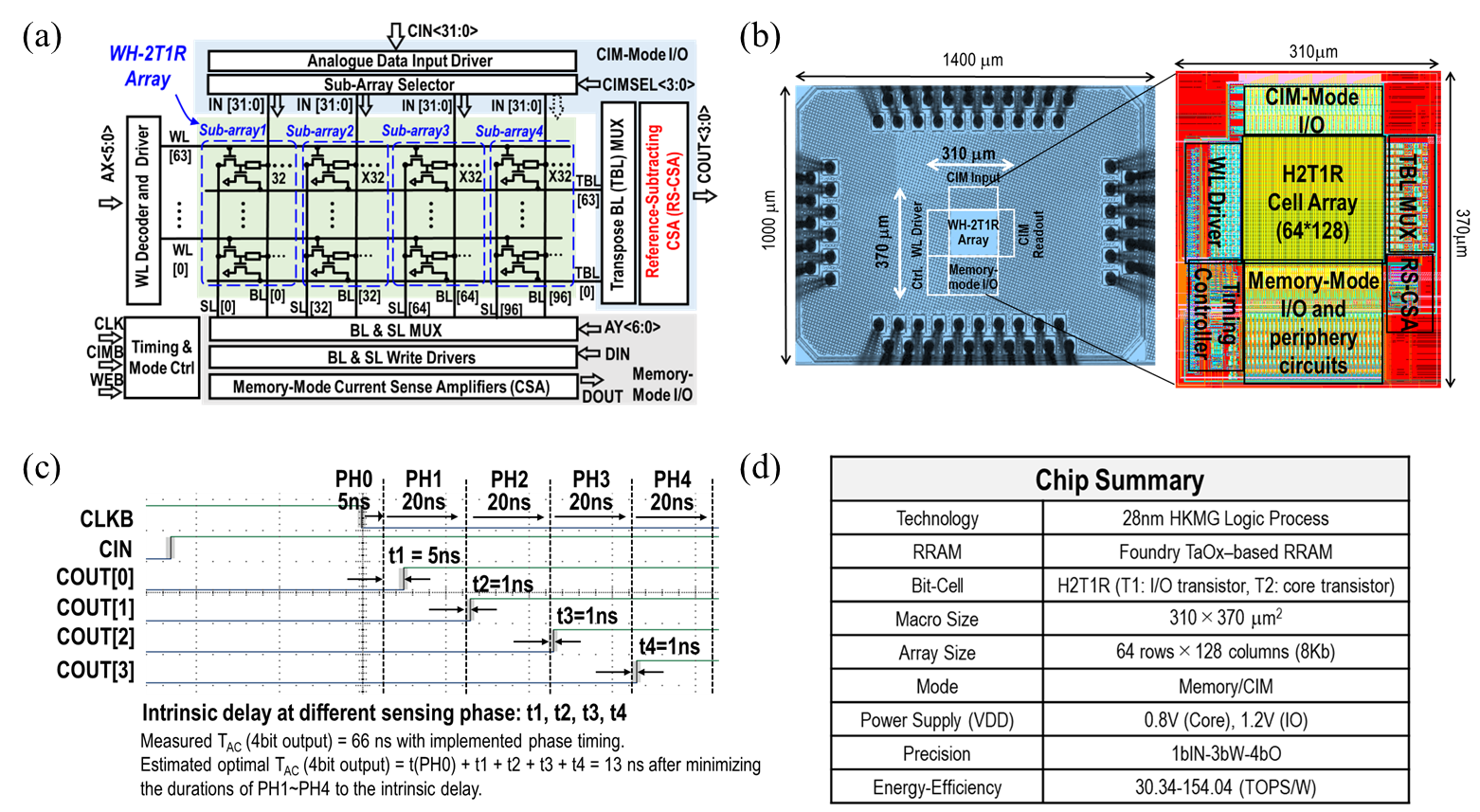

在器件层面,研究团队提出了带权重二晶体管一忆阻器(WH-2T1R)的存算阵列结构。WH-2T1R结构使用core晶体管构成解耦的存算数据通路来减小寄生效应对计算电流的影响,相较1T1R结构只额外造成30.3%的面积开销。计算单元利用第二晶体管亚阈值区放大特性提高计算13.5倍开关比的同时降低88%的低阻态计算电流,从而实现了63.4%的乘加操作功耗降低。得益于计算开关比的提升,该RRAM存内计算结构可支持更高的输入并行度和多比特乘加操作。

在电路层面,研究团队提出了参考电流减式电流型灵敏放大器的读出电路。由参考电流减支路根据上一次读出结果先对输入电流进行电流减再送到电流镜读出数据。参考电流减支路对半减小了电流镜输入电流范围,使RRAM存算结构支持的计算电流范围倍增,能实现更高输入并行和多比特乘加,并取得79.5%的读出电路功耗降低。研究团队通过进一步优化电流型灵敏放大器电流减配置,实现积分非线性误差5倍提升,微分非线性误差3.75倍提升。

在算法映射层面,研究团队提出了高位数据冗余(MSB_RSM)的映射策略。RRAM存内计算结构配备有不同第二晶体管multiplier参数的多组阵列和额外的一组冗余阵列。其中不同第二晶体管用于映射多比特权值的不同比特位。由于RRAM和晶体管非理想因素对计算电流的影响不容忽视,冗余阵列用于额外映射权值对非理想因素补偿。经过对不同比特位补偿效果的分析,MSB-RSM对高位权值进行操作时能减小1σ误差40%。得益于更稳定的计算电流,在ResNet-18模型下的CIFAR-10和CIFAR-100任务获得了0.96%和2.83%的准确度提升。

上述方案在团队自主开发的嵌入式28nm 工艺上得到验证,新型RRAM存内计算结构支持高并行的模拟域乘加操作,在1比特输入、3比特权值、4比特输出下ResNet-18任务中的平均能效达到30.34TOPS/W,并可以通过进一步优化读出时序提升到154.04TOPS/W。该工作通过单元、电路及系统面的系统设计,为高能效、高精度的模拟存内计算提供了新思路。

研究成果以“A 28nm RRAM Computing-in-Memory Macro Using Weighted Hybrid 2T1R Cell Array and Reference Subtracting Sense Amplifier for AI Edge Inference”为题发表在集成电路设计领域旗舰期刊IEEE Journal of Solid-State Circuits上,微电子所博士研究生叶望为该文章的第一作者、窦春萌研究员为该文章的通讯作者。

(a)基于RRAM的存内计算芯片结构框图,(b)芯片晶圆照片及版图,

(c)芯片测试数字波形,(d)芯片参数

| 相关新闻: |

| 微电子所在铁电存储器可靠性研究方面取得进展 |

| 微电子所在单细胞电学特性流式分析方法及分析仪器研究方面取得新进展 |

| 微电子所在氧化铪基铁电存储材料方面取得重要进展 |

学习园地