近日,微电子所新技术开发部微系统技术实验室焦斌斌研究员团队在高密度低应力硅通孔(TSV)研究方面取得新进展。

三维(3D)集成技术是制造低功耗、高性能和高集成密度器件的必备技术,有望突破摩尔定律限制。TSV作为3D集成的核心技术,具有缩短互连路径和减小封装尺寸的优势。目前,高密度TSV互连在近传感器和传感器内计算、混合存储器立方体、高带宽存储器(HBM)、互补金属氧化物半导体(CMOS)图像传感器、制冷和非制冷焦平面阵列、有源像素传感器等具有重要应用前景。但在高密度应用场景下,由于硅衬底与TSV互连金属之间热膨胀系数不匹配,TSV存在严重的热应力问题,会导致晶体管迁移率和参数偏移进而影响器件性能,甚至导致器件损坏,亟需通过结构调控抑制热应力对器件可靠性的影响。

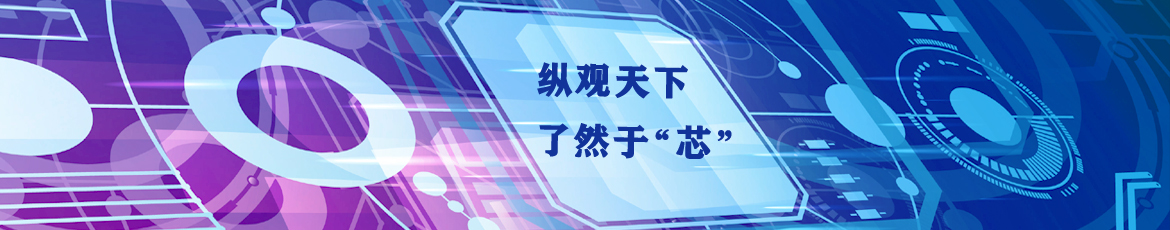

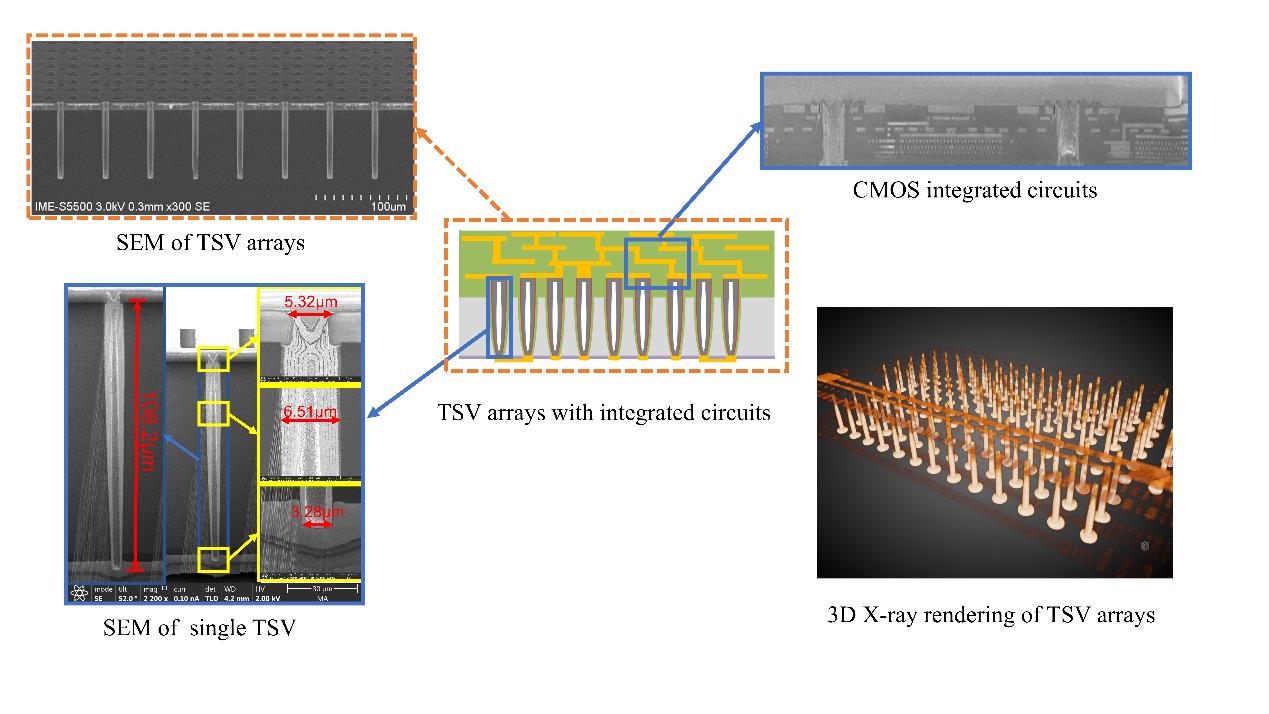

焦斌斌团队创新性提出了两端窄中间宽、两端封闭中间空心的“类橄榄球”状TSV结构,具有小孔径、高深宽比、低应力等特点。向内溃缩的应力缓冲空心结构为TSV提供了应力释放空间,可大幅降低衬底硅的应力和电迁移,可耐受大温差使用工况,两端封口结构兼容后续传统旋涂涂胶工艺,具有普适性。目前已实现了国际已有报道中深度最大(>100μm)、深宽比最大(>20.3:1),残余应力最小(31.02MPa)的TSV结构,其直径5μm、中心距 25μm、TSV数量达320000(密度1600个/mm2),有效连通率达100%,是唯一可耐受极低温工况(-200℃)的TSV解决方案。

基于该成果的论文“Low-Stress TSV Arrays for High-Density Interconnection”近期发表在中国工程院院刊Engineering(2095-8099,2095-8099,https://doi.org/10.1016/j.eng.2023.11.023)。微电子所焦斌斌研究员为论文第一作者兼通讯作者,乔靖评博士为论文第二作者。该研究成果同时被2023 IEEE 73rd Electronic Components and Technology Conference (ECTC)会议收录,并以分会场报告的形式展示。

Engineering期刊瞄准世界科技前沿,服务国家重大战略需求,面向人民生命健康,聚焦具有重大经济、社会意义和世界先进水平的工程科技原创性成果,内容涉及全球重大挑战、人工智能、新冠病毒肺炎、碳中和、6G等工程科技前沿热点,引领工程科技各前沿领域的发展。

Electronic Components and Technology Conference (ECTC)是汇聚封装、元件和微电子系统科学、技术和教育领域最佳合作与技术交流环境的顶级国际盛会。

论文链接:https://www.sciencedirect.com/science/article/pii/S209580992400153X

高密度互连的低应力TSV设计与制备

| 相关新闻: |

| 微电子所在光刻胶模型校准研究方面取得重要进展 |

| 微电子所在片上学习存算一体芯片方面取得重要进展 |

| 微电子所在数模混合存算一体芯片方面取得重要进展 |

学习园地