人工智能的飞速发展对计算和存储等硬件资源提出了巨大需求,迫切需要提升存储器层级访问的性能与效率。当前,主流计算硬件的存储系统由片上静态随机访问存储器(SRAM)以及片下随机动态存储器(DRAM)构成,它们之间通过有限的总线来进行数据传递,导致带宽有限、功耗与延迟较大等问题,逐渐成为大数据、高算力等人工智能应用的瓶颈。此外,传统硅基六晶体管型(6-T)SRAM单元因其较大的特征尺寸和待机漏电问题,在密度和能耗方面存在诸多限制。同时,传统的硅基DRAM单元也面临着数据保持时间较短、无法通过后道集成提升存储密度等问题,这些问题从根本上限制了SRAM-DRAM存储系统的功耗与密度。

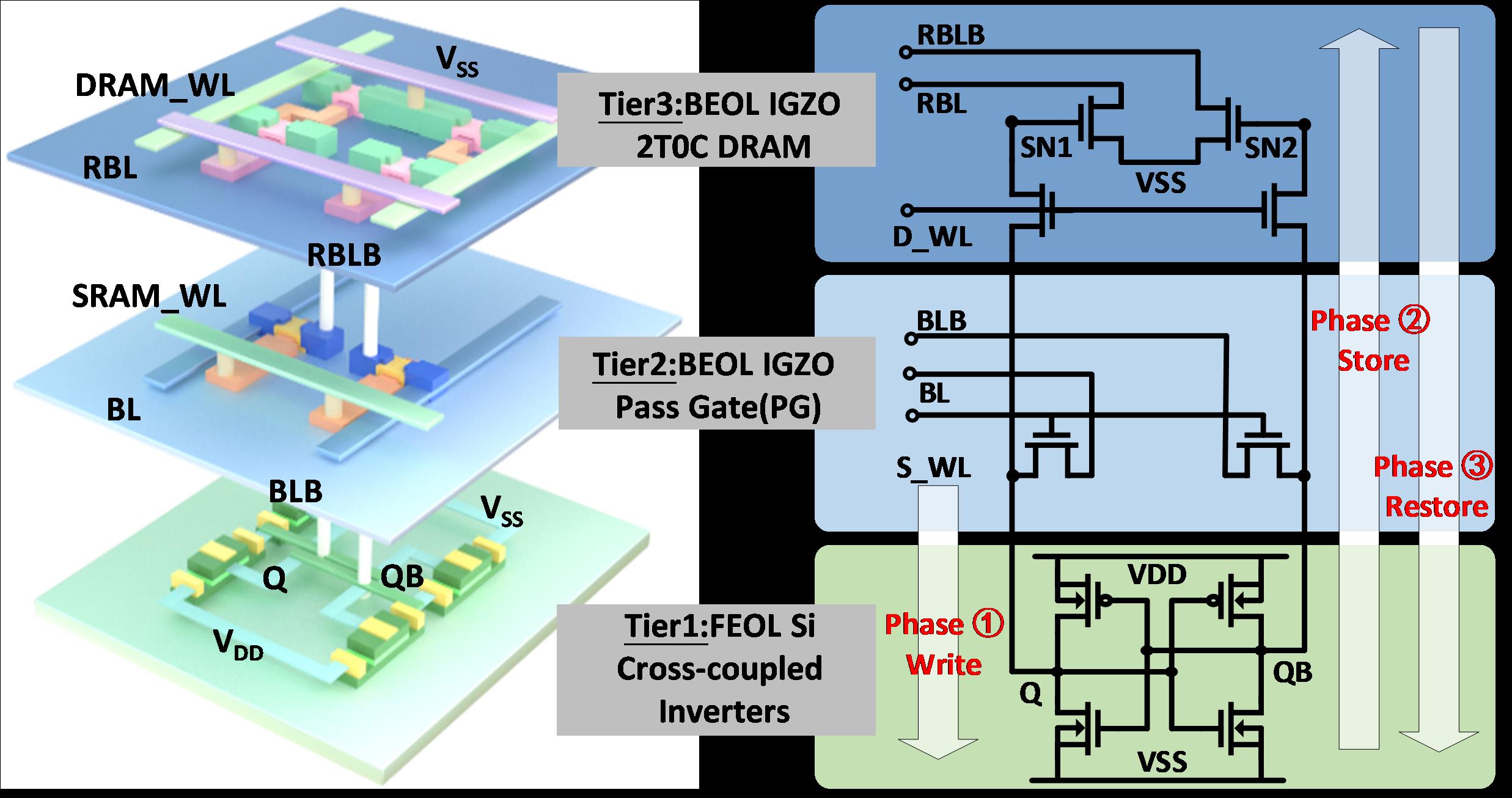

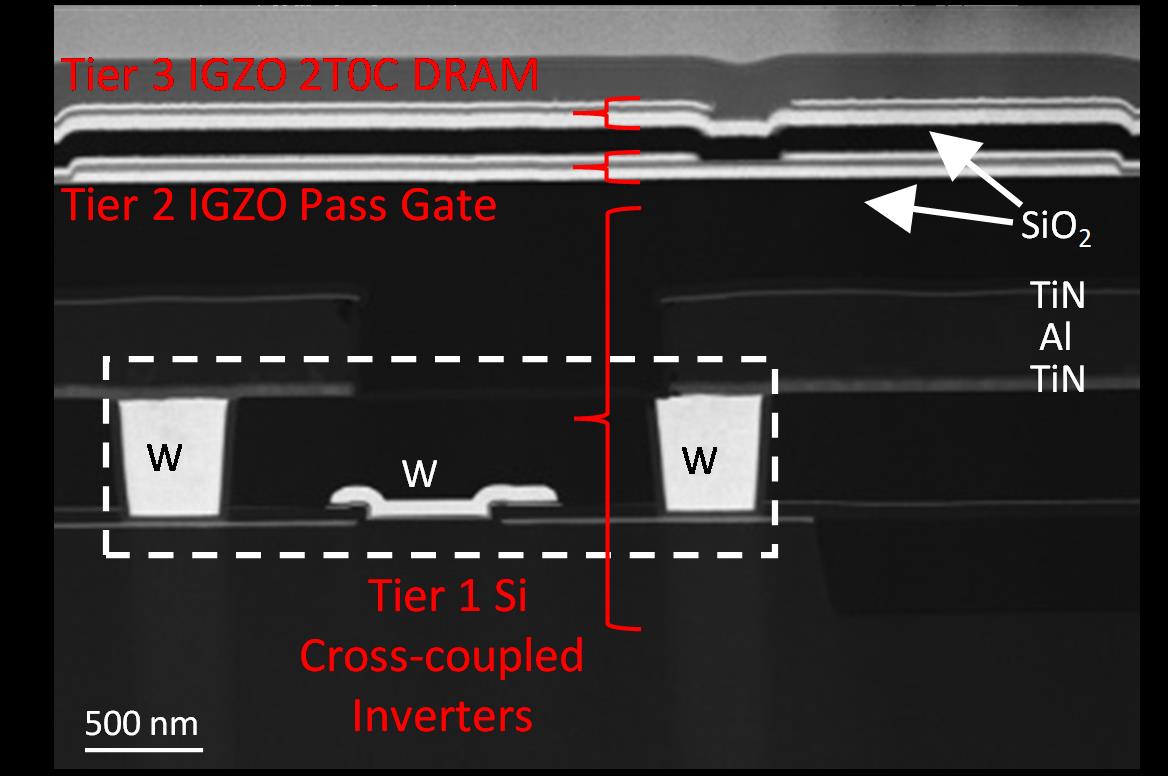

针对上述问题,微电子所集成电路制造技术重点实验室刘明院士/李泠研究员团队通过多层堆叠IGZO薄膜晶体管(TFT)与硅基电路后道集成,提出了一种新型IGZO/Si SRAM和IGZO 2T0C DRAM的三维存储结构,成功实现了高密度、低能耗和高速数据传输等特性。在该结构中,通过在前道硅基闩锁结构上后道集成IGZO传输门,有效地减少了SRAM的占用空间和待机功耗。此外,基于垂直堆叠三层间互连结构,实现了SRAM-DRAM数据传输的最低延迟(<10ns)和最低能耗(2.26fJ)。同时,IGZO 2T0C DRAM的高数据保持特性使SRAM能够在长时间断电(>5000s)后不丢失数据以降低待机功耗。

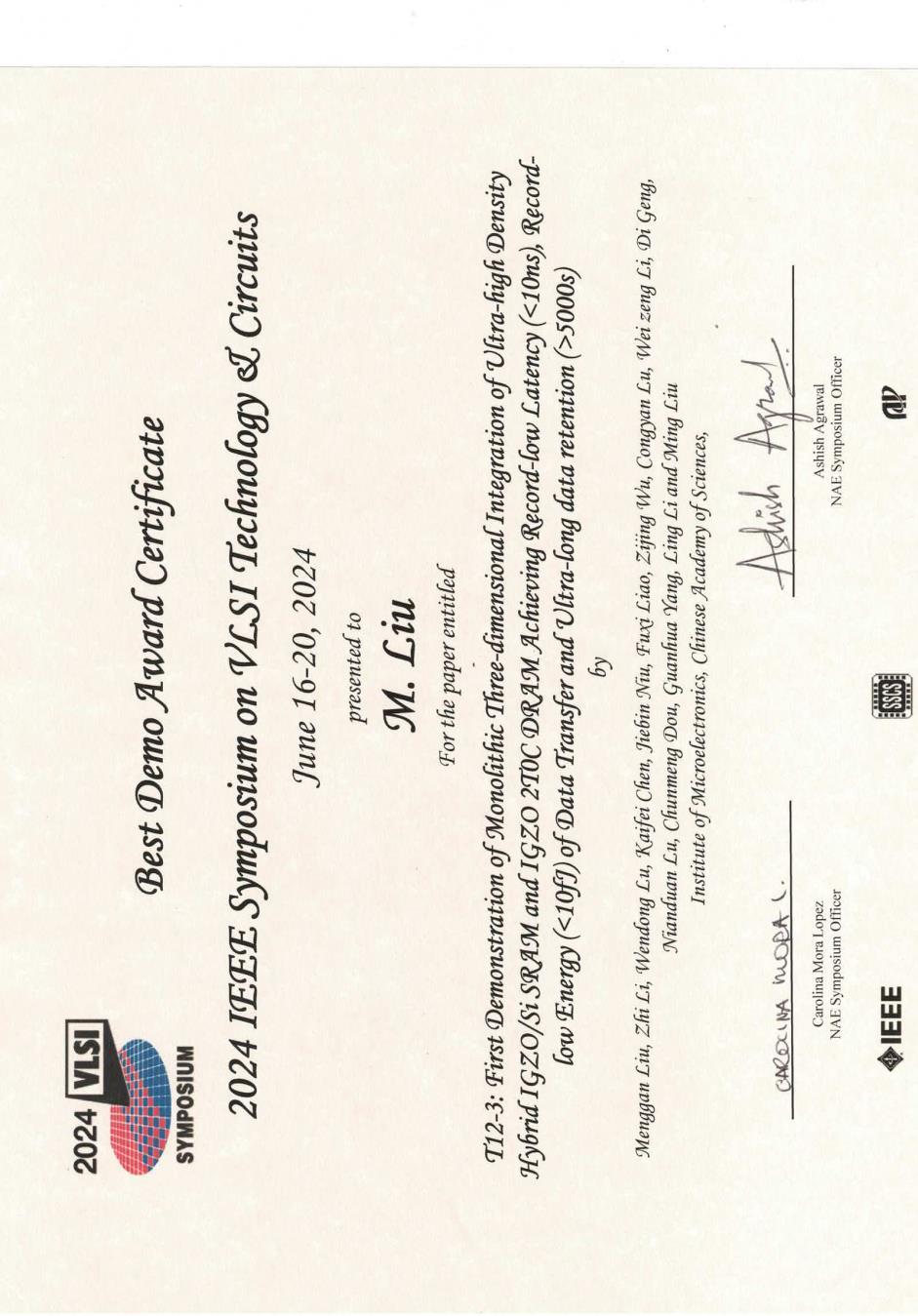

上述研究成果以题为“First Demonstration of Monolithic Three-dimensional Integration of Ultra-high Density Hybrid IGZO/Si SRAM and IGZO 2T0C DRAM Achieving Record-low Latency (<10ns), Record-low Energy (<10fJ) of Data Transfer and Ultra-long data retention (>5000s)”的论文入选2024 VLSI,并获得大会Best Demo Paper Award奖项。该奖项每年只颁发2项、分别由工艺与电路分论坛各推选1项,本工作也是大陆首次获得该奖项。微电子所博士生刘孟淦、李智和卢文栋为共同第一作者,微电子所李泠研究员、杨冠华副研究员以及窦春萌研究员为通讯作者。

图1 采用三层堆叠的三维集成M3D-SRAM-DRAM结构和对应的电路以及TEM电镜图

图2 混合IGZO/Si 4T SRAM与传统6T SRAM在面积和能耗上的对比;

M3D-SRAM-DRAM系统与传统SRAM+DRAM系统在传输延时和能耗上的对比

图3 Best Demo Award奖项

| 相关新闻: |

| 微电子所在存内计算处理器上取得进展 |

| 微电子所在新结构p-GaN栅极HEMT器件和电路级可靠性研究方面取得重要进展 |

| 微电子所在全自旋神经形态计算硬件研制及电路实现方面取得新进展 |

学习园地