近年来,二维半导体已成为解决高尺寸晶体管中通道控制问题的主要潜在解决方案。随着器件的缩小,通道厚度应按比例缩小。否则,栅极电容将不足以控制电流的流动。不幸的是,陷阱和其他界面缺陷会降低载流子迁移率,并且在薄通道中更为重要。硅通道厚度的实际极限似乎约为 3nm。

斯坦福大学研究员 Aravindh Kumar 在一次采访中解释说,二维过渡金属二硫化物 (TMD),如 MoS2和 WSe2,之所以有趣,是因为它们没有平面外的悬空键。顶部和底部表面的相互作用是有限的,对载体行为几乎没有影响。特别是MoS2,易于合成且非常稳定。

尽管如此,TMD 沉积通常需要非常高的温度,远高于通常使用的底栅结构的公差。例如,在imec,研究员 Yuanyuan Shi 及其同事使用 1000°C MOCVD 工艺进行 MoS2沉积。出于这个原因,大多数关于 TMD 器件的研究要么使用从散装材料剥离的薄片,要么使用在蓝宝石或二氧化硅上生长然后转移的独立层。

虽然层转移方法允许器件研究与工艺开发并行进行,但低温硅兼容沉积工艺对于 TMD 器件的商业化至关重要。在 12 月的 IEEE 电子设备会议上报告的工作中,英特尔高级研究工程师 Kevin O'Brien 和他的同事使用预先图案化的金属氧化物晶种来创建 WS2生长的成核位点。将金属源直接放置在晶片上避免了使用固体金属氧化物 CVD 源。受控成核限制了TMD 晶体的位置,因此限制了与它们相关的晶界。

独立式 MoS2片材的质量取决于沉积工艺和原始基板。例如,在 ACS Nano 中,苏塞克斯大学的研究员 Manoj Tripathi 及其同事报告说,通过 CVD 在二氧化硅基底上生长的MoS2处于张力状态,因为它在冷却过程中比二氧化硅收缩得更多。储存的张力防止了皱纹的形成,这是剥落的 MoS2中的常见问题。

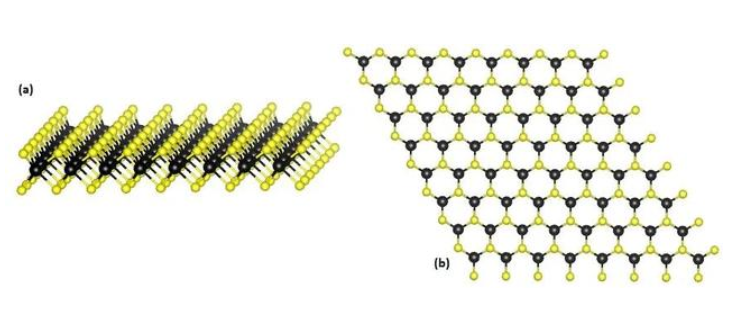

图1:过渡金属二硫属化物单层的晶体结构:(a) 侧视图,(b) 俯视图

优化器件结构

随着薄膜的生长,进入的分子自然会呈现出最有利的结构。在 MoS2中,直接沉积在蓝宝石上仅比沉积在预先存在的 MoS2表面上更有利。结果,具有多个MoS2层的岛可以在与衬底接触的层完成之前形成。这些岛屿的边缘确实有悬空键,尽管使它们更具反应性。Shi 的 imec 小组通过使用沉积后 Cl2蚀刻来优先去除生长岛,从而利用边缘反应性。岛的去除提高了在蓝宝石上生长的 MOCVD 薄膜的表面粗糙度和厚度均匀性。

正如硅器件的未来可能依赖于堆叠纳米片一样,TMD 晶体管可能需要多个堆叠通道来承载足够的电流。北京大学教授熊雄及其同事通过转移两个大型独立单分子层,然后将材料蚀刻到所需的器件尺寸,制造了堆叠的 MoS 在单个堆栈中使用 MoS2通道。相同的工艺也可用于制造堆叠互补 FET,例如用于 NMOS 和 WSe2用于PMOS。

如上所述,目前最好的 MoS2器件取决于背栅设计,其中栅极金属和栅极氧化物沉积在硅衬底上,然后在顶部放置MoS2层。这种方法提供了更好的设备性能,但最终顶栅设备更具可扩展性。与环栅硅晶体管一样,具有匹配顶部和底部电容的双栅将比单栅提供更好的通道控制。Imec 器件集成工程师 Xiangyu Wu 及其同事使用 GdAlOx中间层来改善双栅极 MoS2器件中的电容匹配。中间层似乎可以减少短沟道效应并改善阈值电压控制。

制造独立式 MoS2薄膜的工艺现在已经足够成熟,可以生产出统计上有用的设备数量。研究人员现在正在报告数千台设备的统计数据,这是可扩展过程的先决条件。不幸的是,这数以千计的设备仍然落后于硅的性能基准。与 TMD 的联系尤其具有挑战性。

进行接触

接触电阻似乎有两个来源。缺陷引起的间隙状态来自于在 MoS2沉积期间或在金属接触形成期间产生的表面缺陷。台积电的工作在沉积过程中使用氧气来钝化硫空位,这是缺陷的一种来源。Kumar 提出,来自热激发接触金属的物理轰击也有助于增加接触电阻。斯坦福大学的工作使用了锡和铟,它们是低熔点材料,可以以最小的损坏进行沉积。当用金覆盖时,这些金属形成在 450°C 以上稳定的合金,使其与现有的 BEOL 工艺兼容。

金属诱导的间隙状态是接触电阻的另一个贡献者,导致费米能级钉扎。当费米能级被钉扎时,界面处的能垒高度与接触金属的功函数无关,不能用于调节阈值电压。半金属作为潜在接触很有趣,因为它们在费米能级上没有带隙和低态密度。因此,它们往往不会产生 MIGS。在半金属中,铋和锡的熔点较低,分别为 271.5°C 和 231.9°C。锑的熔点为 630.6°C,更适合工艺。在 TSMC 提出的工作中,Ang-Sheng Chou 建议将 40% 或更多的锑与铋合金化可以实现接触势垒高度、合金导电性和熔点的共同优化。例如,

虽然英特尔集团的最佳联系人也使用锑,但他们警告说,MoS2 NMOS 器件远远落后于硅基准,在目标亚阈值摆动值下,电流比硅低 3 倍。对于WSe2 PMOS 器件,情况更糟。他们最好的器件使用钌触点,在 141 mV/decade 的亚阈值摆幅下实现了 50 μA/μm 的电流。

大多数 2D 半导体 FET 演示都使用顶部触点,因为它们更容易制造。不过,边缘触点更小,这可以减少整体器件的占用空间,也可以减少通道长度的积极缩放。此外,如上所述,2D 材料的边缘确实具有悬空键。与顶部触点中存在的弱范德华键相比,边缘触点可能形成共价键。台积电的 Terry Hung 在 2020 年 IEDM 上展示的工作表明,边缘接触消除了费米能级钉扎。界面表面(二维材料边缘的"中间线")形成一个偶极子,其效应随着距离的增加而迅速衰减。

结论

总体而言,二维半导体器件的前景充其量是喜忧参半。虽然最近的研究表明材料生长和触点制造方面取得了重大进展,但尚未证明可以与前沿硅竞争的设备。当它们确实出现时,它们很可能涉及与当前晶圆厂不同的材料和工艺。

| 相关新闻: |

| 单原子厚二维磁铁可在室温下工作 |

| 量子气体中首次实现二维超固体 |

| 二维材料首现奇异“多铁性”状态 |

学习园地