近日,中国科学院微电子研究所集成电路先导工艺研发中心在面向5纳米以下技术代的新型硅基环栅纳米线(Gate-all-around silicon nanowire,GAA SiNW) MOS器件的结构和制造方法研究上取得重要进展。

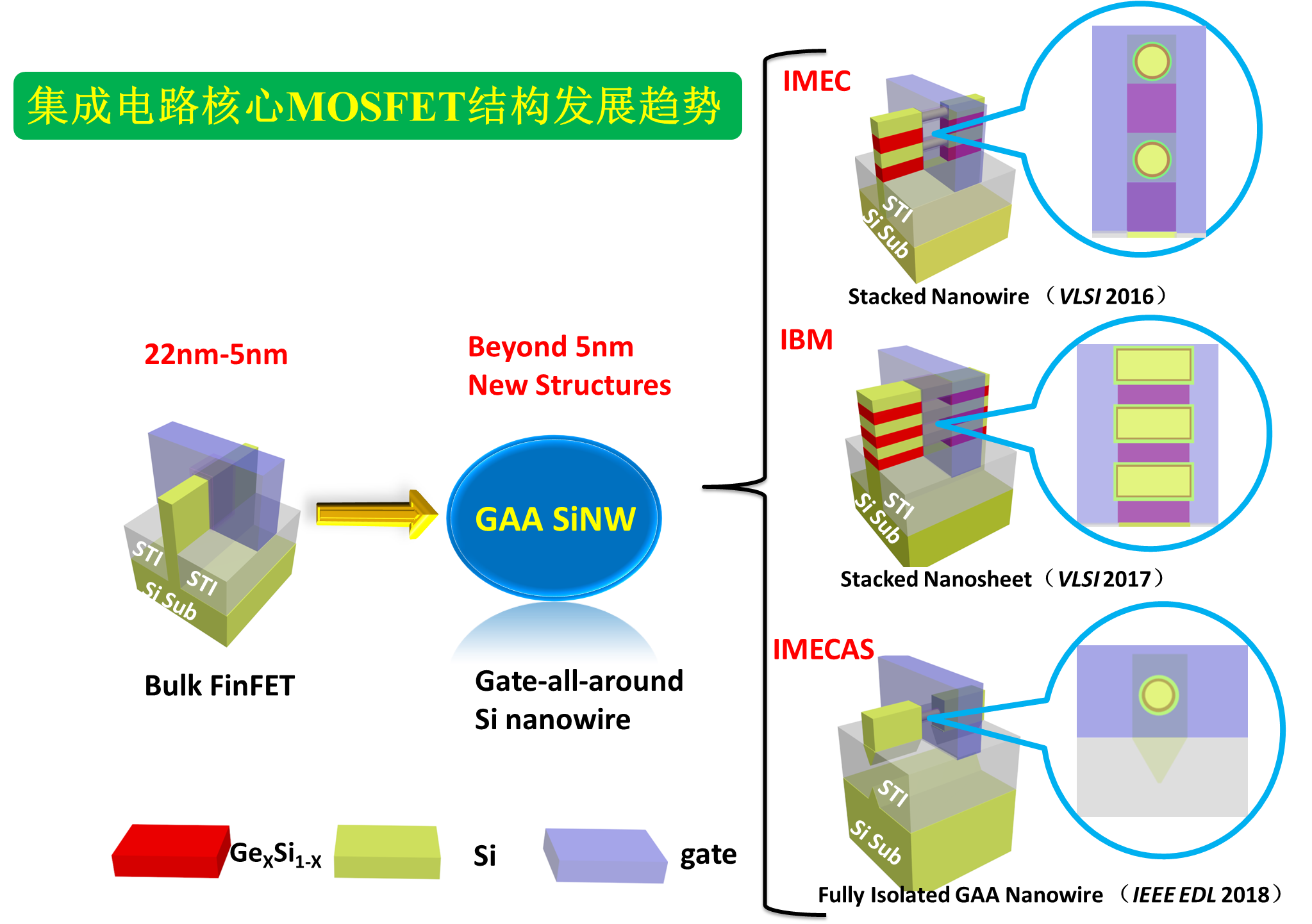

5纳米以下集成电路技术中现有的FinFET器件结构面临诸多挑战。环栅纳米线器件由于具有更好的沟道静电完整性、漏电流控制和载流子一维弹道输运等优势,被认为是未来可能取代FinFET的关键架构之一。近年来,将理想环栅纳米线结构和主流FinFET工艺结合发展下一代集成技术已成为集成电路深入发展的研发关键热点之一。如图1所示,目前国际报道的基于主流高k金属栅FinFET制造工艺形成堆叠纳米线器件的研发有两种不同方案:堆叠纳米线(SNW,IMEC)和堆叠纳米片(Nanosheet,IBM)技术。上述方案都需要在普通硅衬底上外延生长高质量的多层GeSi/Si结构,并在高k金属栅取代栅工艺中选择腐蚀GeSi或Si,最终在沟道中选择形成堆叠纳米线而在源漏中保持Fin结构。该技术在集成电路大规模制造中存在许多潜在的挑战: 须生长高质量、接近体硅质量无缺陷的多层GeSi/Si外延层;由于Ge元素在最前道集成步骤中引入,给后继工艺带来较低的工艺温度窗口限制以及较多的Ge原子沾污机会。

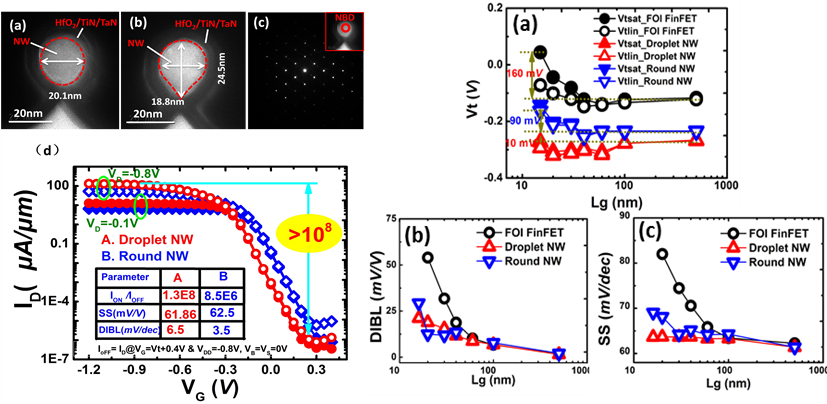

针对上述纳米线晶体管架构在集成电路发展应用中所面临的难题,殷华湘研究员研发团队提出在主流硅基FinFET集成工艺基础上,通过高级刻蚀技术形成体硅绝缘硅Fin和高k金属栅取代栅工艺中选择腐蚀SiO2相结合,最终形成全隔离硅基环栅纳米线MOS器件的新方法。并在取代栅中绝缘硅Fin释放之后,采用氧化和氢气退火两种工艺分别将隔离的“多边形硅Fin”转化成 “倒水滴形”和“圆形”两种纳米线结构。由于在该方法中,纳米线沟道由单晶硅衬底制作形成,导电沟道中材料晶格缺陷更少、界面质量更高。两种高k金属环栅纳米线晶体管都表现出很好的器件特性,其中通过氧化制备的“倒水滴形”环栅纳米线晶体管在16nm物理栅长(对应5nm及以下技术代)下,获得器件亚阈值特性SS = 61.86 mV/dec 和DIBL = 6.5 mV/V,电流开关比大于1E8。SS和DIBL十分接近MOSFET的理论极限数值(60mV/dec和0 mV/V),远超以往同类工艺制造的FinFET性能参数,也达到目前同类器件所报道的最高水平。同时,该类器件结构也可以通过同样的方法在多步刻蚀和取代栅工艺中制作成多层堆叠纳米线,该项研究工作正在进行中。这种不同于现有国际报道的制造方法具有完全自主知识产权,可为未来我国集成电路下一代关键技术的创新发展提供核心器件架构和制造工艺开发的多样选择。该工作以《通过一种先进工艺形成具有优异短沟道控制能力的新型p型环栅纳米线场效应晶体管》为题发表在国际微电子器件领域顶级期刊《IEEE电子器件快报》上(IEEE Electron Device Letters,DOI: 10.1109/LED.2018.2807389),并被选为该期期刊首篇论文。

该项研究得到国家科技重大专项02专项和国家重点研发计划等项目的资助。

图1. 集成电路核心MOS器件结构发展趋势

图2. 研制的全隔离硅基环栅纳米线MOSFET结构与电学特性

综合信息