受制于传统冯诺依曼架构下“存储墙”问题,芯片的算力难以进一步提升,限制了大数据以及人工智能等新兴信息技术产业的发展。存内计算是非冯诺依曼架构下提高芯片算力的一种有效途径,基于铁电晶体管(Fe-FET)的存算融合电路由于具有低功耗、高CMOS兼容性以及无损读出等优点,被认为是极具潜力的一种存内计算的技术方向。现已报道的Fe-FET存算电路多为单模机制。实现逻辑门电路往往需要多器件集成,或外围电路辅助来获得高效的存算功能。且在实现存算单元电路的重构过程中面临方案复杂、重构逻辑种类有限的挑战。

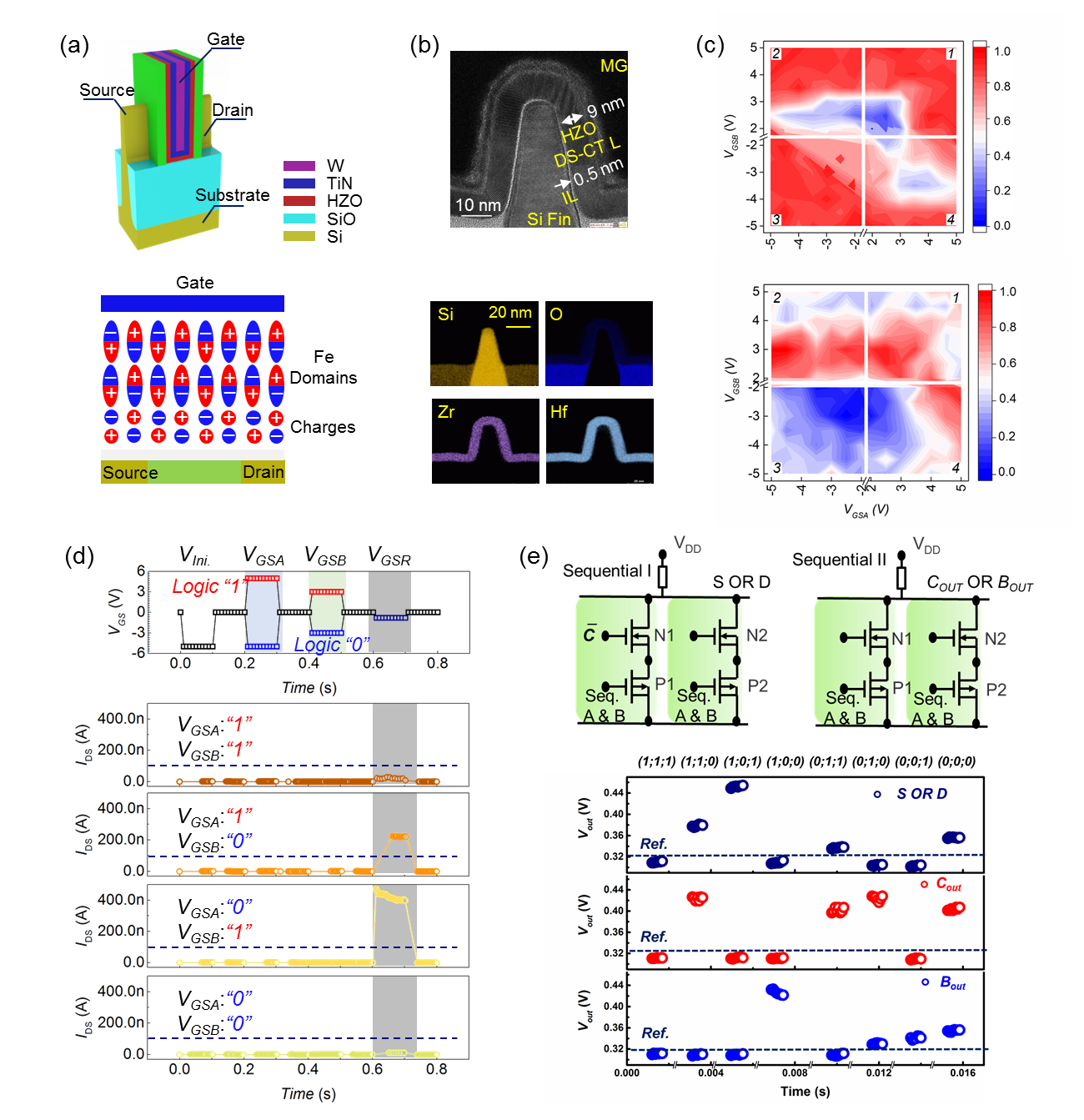

中科院微电子所集成电路先导工艺研发中心殷华湘研究员团队提出一种同时实现电荷俘获(CT)与铁电极化反转(PS)耦合的新型多模态Fe-FinFET存算一体器件。通过时域连续栅压VGSA与VGSB变化实现晶体管CT与DS空间上的耦合运算,获得基于Fe-FinFET的单器件(1T)存算一体单元电路。进而通过改变栅压幅值或脉宽,实现对晶体管CT与DS耦合幅度调控,获得不同的沟道电导分布,实现可重构的多种布尔逻辑运算。基于此新机制,研究团队成功在2T单元电路上获得全部16种布尔逻辑运算,并应用该技术,在4T单元上实现了可重构的一位加法器和减法器算术逻辑运算功能。相比基于常规CMOS晶体管的传统功能电路(仅加法器需要30T)大幅减小了硬件开销并显著提升能效,为未来后摩尔极低功耗器件和电路技术突破提供了一种创新技术方案。

该成果近日以“A Polarization-Switching, Charge-Trapping, Modulated Arithmetic Logic Unit for In-Memory Computing Based on Ferroelectric Fin Field-Effect Transistors”为题发表在国际著名期刊《ACS Applied Materials & Interfaces》上(DOI: 10.1021/acsami.1c20189,中科院一区)。微电子所张兆浩助理研究员为该文第一作者,殷华湘研究员、张青竹副研究员为该文通讯作者。

该研究得到了国家自然科学基金后摩尔重大研究计划及青年项目的资助。

图(a)新型PS-CT多模态存算一体FinFET器件结构及原理;(b)结构TEM表征图;(c)p以及n型可重构PS-CT存算一体器件在不同VGSA与VGSB输入组合下获得的不同沟道电导分布图;(d)基于1T p型PS-CT FinFET实现XOR布尔逻辑运算的操作方案及电学结果;(e)基于4T的可重构加/减法器算术逻辑运算单元构建方案及电学结果

综合信息