近日,中科院微电子所先导中心在美国电化学会《固态科学与技术杂志》发表了文章:Study of Isotropic and Si-Selective Quasi Atomic Layer Etching of Si1-xGex (DOI:10.1149/2162-8777/AB80AE),文章系统介绍了一种全新的集成电路刻蚀技术:各向同性和硅选择性的锗硅准原子层刻蚀技术(quasi- Atomic Layer Etching),下文简称为qALE。

当前芯片制造已步入5纳米节点,随着集成电路不断微缩,工艺技术面临极大挑战,原子层刻蚀工艺(atomic layer etching,ALE)是近年重新兴起的技术,通过循环使用形成自限制的表面改性层并将其选择性去除的方式在原子尺度逐层去除材料。ALE技术具有精确的刻蚀控制、良好的均匀性、小的负载效应等优点,越来越受到重视而重新成为研究热点。目前ALE的主流还是等离子体刻蚀技术,包括常温的各向异性ALE和高温的各向同性ALE等。不过ALE技术并不完全成熟,而且ALE工艺时间长,产能低,另外在面向3纳米以下新三维结构、材料和器件时,ALE仍然缺少解决方案。

先导中心朱慧珑课题组于3年前发明了一种准原子层刻蚀技术并进行了较系统的研究,该技术面向3纳米以下的环栅纳米结构,研发了各向同性的、对硅具有较高选择性的锗硅准原子层刻蚀技术,并研究了多种工艺方法、影响因素和刻蚀机理,围绕相关技术进行了专利布局。

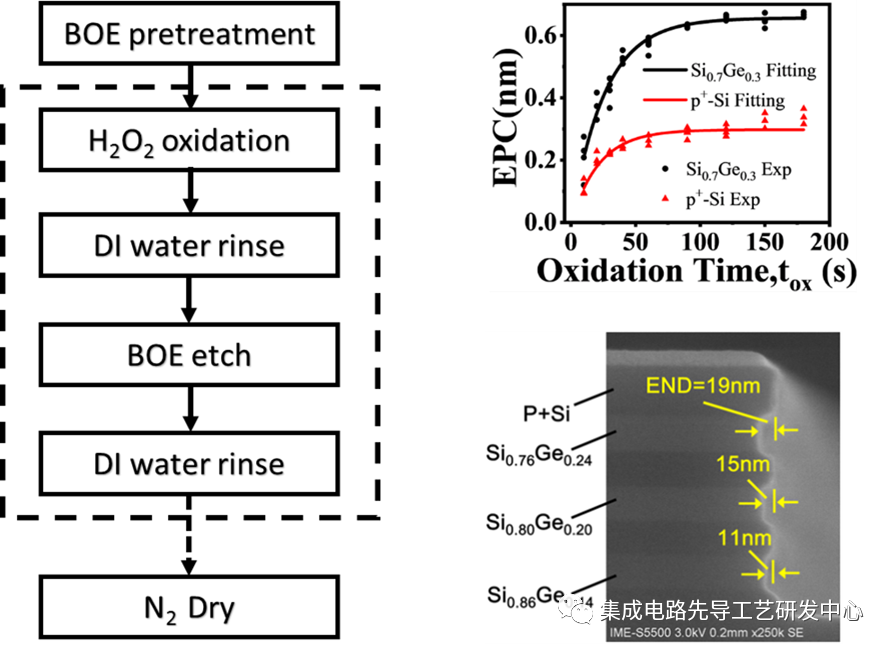

所研发的准原子刻蚀通过准自限制的氧化并将其选择性去除的方式,根据锗硅和硅被氧化的程度不同,达到选择性刻蚀锗硅的目的,刻蚀量精确可控。此方法具有工艺窗口大、工艺波动小、负载效应小以及各向同性的优点,从而适用于高密度复杂三维结构的刻蚀。此外 qALE 操作简单、成本低、可批量操作,因而具有用于大规模 IC 制造的潜力。

图1

利用新的qALE技术,先导中心已经实现了首个具有自对准栅极的叠层垂直纳米环栅晶体管(VerticalSandwich Gate-All-Around FETs, VSAFETs),获得多项中、美发明专利授权,相关成果已经发表在《IEEE Electron Device Letters》上(DOI:10.1109/LED.2019.2954537)。

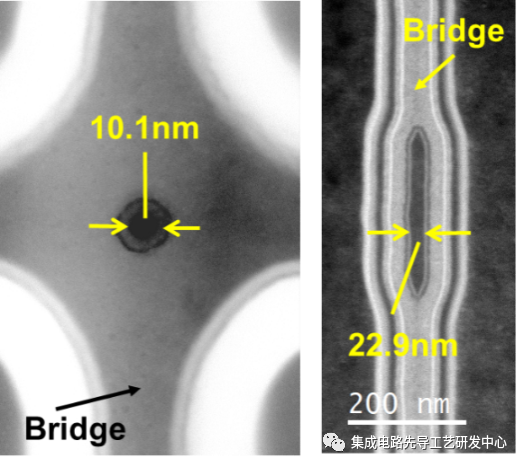

图3 STEM俯视图:qALE方法制备的直径10纳米的锗硅纳米线(左)和厚度23纳米的锗硅纳米片(右)

图4 TEM截面图:qALE方法制备的具有自对准高K金属栅的VSAFET晶体管

计算光刻中心