近期,微电子所感知中心低功耗智能技术与系统团队在低功耗集成电路设计领域取得新进展,设计了兼容近/亚阈值工作区的基础电路单元,可以广泛应用于低功耗智能计算芯片。

功耗已经成为制约集成电路发展的重要瓶颈。近/亚阈值技术通过将芯片工作电压降低到晶体管的阈值电压附近或者阈值电压以下,可以大幅降低数字系统的功耗。近/亚阈值基础数字电路单元是低功耗智能计算芯片的基石,也是本研究重点解决的挑战。

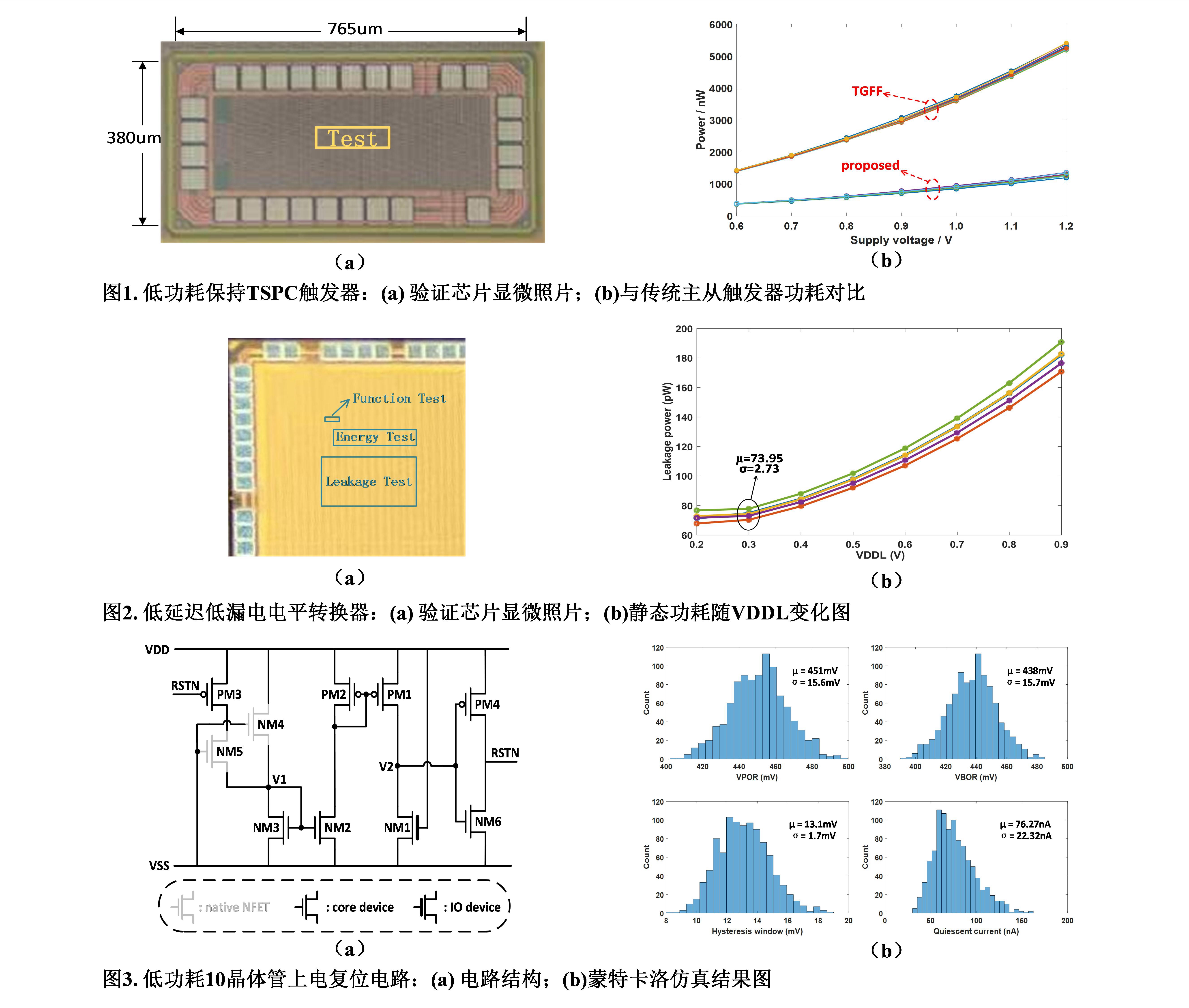

本研究首次提出了领先的零冗余动态功耗触发器、pW级宽范围电平转换器、以及nW级高精度上电复位电路,可广泛应用于低功耗的智能计算芯片。针对传统主从触发器由于冗余操作造成的功耗浪费问题,提出了一种兼容近/亚阈值设计的低功耗保持 TSPC触发器。该触发器采用输入感知预充策略,辅以浮动节点分析和晶体管级优化,有效降低了触发器的功耗。流片结果表明,该触发器功耗相比于传统主从触发器降低了73%。针对传统电平转换器转换范围窄、漏电大、不适用于近/亚阈值设计的问题,提出了一种低延迟低漏电电平转换器。该电平转换器基于电流镜结构,采用混合阈值电流镜技术有效解决了切断直流通路后的节点压降问题,同时采用超截断技术进一步优化了电平转换器的漏电。流片结果表明,该电平转换器支持0.12V-1.2V的电压转换,漏电低至73.95pW。在数字系统中,系统上电和掉电时还需要一个复位信号将系统中的存储单元设置为一个确定的状态。为了保证近/亚阈值下数字系统的稳定工作,需要触发阈值低、阈值偏差小、静态电流小的上电复位电路。针对以上问题,本研究提出了一种低功耗10晶体管上电复位电路。该上电复位电路基于电流参考和电流比较器结构,仅用 10个晶体管即实现了高精度低功耗的上电复位电路。仿真结果表明,该上电复位电路在不同工艺角和温度条件下,触发电压偏差仅为34mV,在0.5V的电源电压下静态功耗低至36nW。

基于以上研究的成果近期先后发表于《IEEE超大规模集成电路与系统汇刊》期刊(IEEE Transactions on Very Large Scale Integration (VLSI) Systems, DOI: 10.1109/TVLSI.2021.3061921)、《IEEE电路与系统汇刊Ⅱ》期刊(IEEE Transactions on Circuits and Systems II: Express Briefs, DOI: 10.1109/TCSII.2020.2980681)以及《2021 IEEE 国际电路与系统研讨会》会议(2021 IEEE International Symposium on Circuits and Systems (ISCAS), DOI: 10.1109/ISCAS51556.2021.9401482)。微电子所博士研究生游恒为上述论文第一作者,微电子所乔树山研究员为上述论文的通信作者。

该研究得到中科院、国家重点研发计划、所长基金等项目资助。

论文链接:

[1] https://ieeexplore.ieee.org/document/9374569

[2] https://ieeexplore.ieee.org/document/9035403

[3] https://ieeexplore.ieee.org/document/9401482

科研工作