在先进集成电路制造工艺中, 纳米环栅器件(GAA)正取代FinFET成为集成电路中的核心器件。垂直纳米环栅器件由于其在减小标准单元面积、缓解栅极长度限制、提高集成密度和改善寄生电容/电阻等方面具有独特优势, 成为先进逻辑和DRAM技术方面的重要研究方向。

微电子所集成电路先导工艺研发中心朱慧珑研究团队于2016年首次提出自对准金属栅的垂直环栅纳米晶体管并对其进行了系统研究,在器件结构、工艺、集成技术及应用等方面获得了一系列进展和突破,研发的VSAFET、 VCNFET、Fe-VSAFET、3D NOR等成果陆续发表在国际微电子器件领域的顶级期刊上,并多次作为封面或“编辑特选”文章。

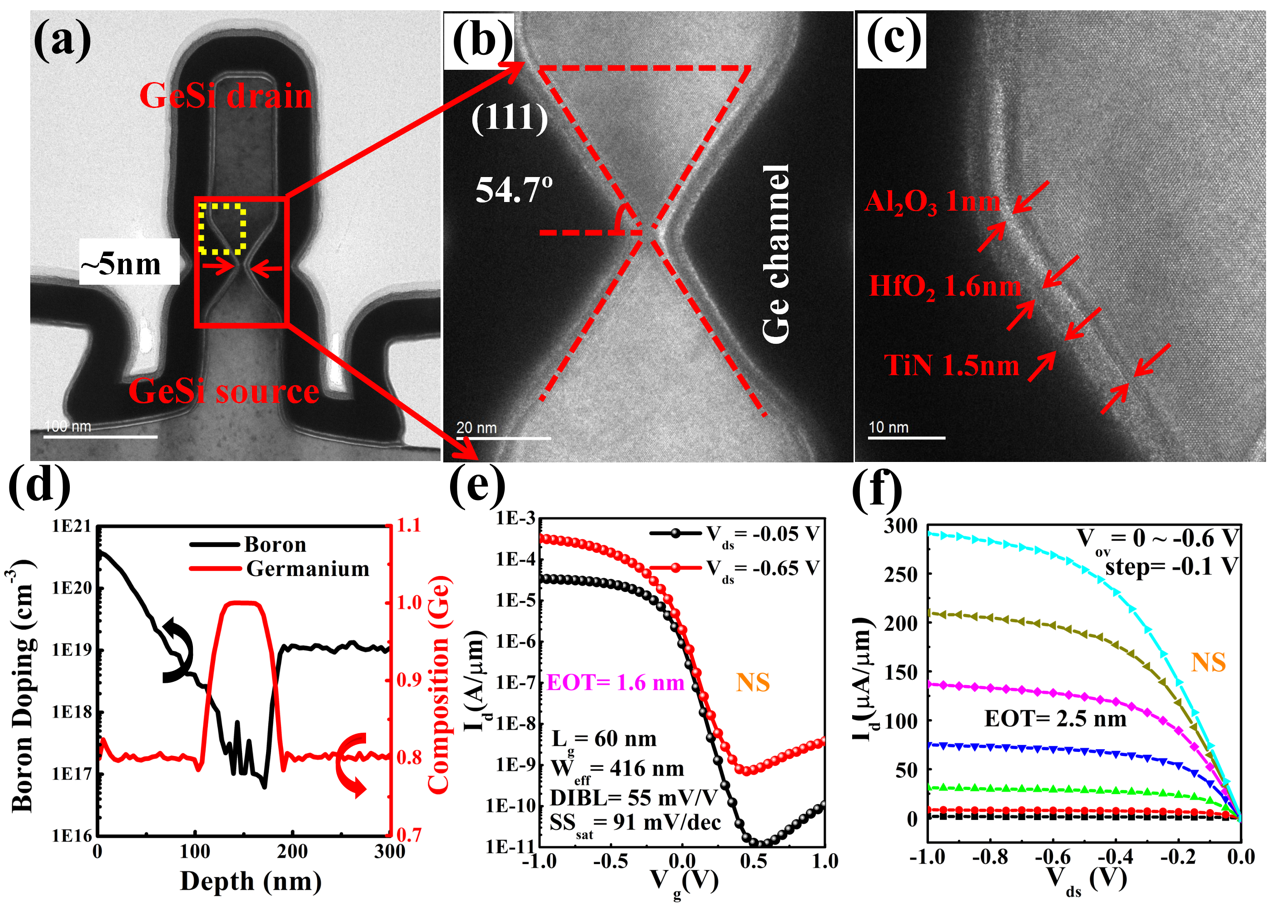

近日,该团队利用自主研发的一种自限制ALE (原子层刻蚀) 工艺, 实现了锗对锗硅材料和晶面的双重选择性精确刻蚀, 制备出了由(111)晶面构成的沙漏型单晶Ge 沟道自对准垂直纳米环栅器件。该沙漏形Ge沟道器件最窄处为5-20nm, 表现出良好的短沟道效应免疫等优异性能, 纳米线器件的开态电流 (Ion)达到291 A/ m,为同类器件最大。该器件同时具有较高的电流开关比(Ion/Ioff = 3.1 106), 良好的亚阈值摆幅 (SS = 91 mV/dec)和漏致势垒降低 (DIBL = 55mV/V)。相关研究成果发表在工程技术类顶级期刊ACS NANO(2023年影响因子/JCR分区:17.1/Q1)上 (DOI: 10.1021/acsnano.3c02518) , 先导中心博士生谢璐为文章第一作者, 朱慧珑研究员与张永奎高级工程师为共同通讯作者。

该研究得到中科院战略先导专项、中科院青年创新促进会、北京超弦存储器研究院和国家自然科学基金等项目资助。

文章链接:https://pubs.acs.org/doi/10.1021/acsnano.3c02518

图 (a) 具有颈缩沟道厚度~5nm的TiN/HfO2/Al2O3/GeOx栅极堆叠的STEM截面, (b) 沙漏形状的Ge沟道在 (111) 平面形成交角54.7 , (c) EOT=1.6nm的栅极堆叠的STEM图像, (d)漏极离子注入尖峰退火后Ge和B的SIMS分布, (e) EOT=1.6nm 的Ge沟道p型垂直环栅纳米线器件的Id-Vg转移特性曲线, (f) EOT=2.5nm 的Ge沟道p型垂直环栅纳米线器件的典型Id-Vds输出曲线

科研工作