全环绕栅(GAA)器件具有极佳的栅控特性、更高的驱动性能以及更多的电路设计灵活性,是主流集成电路制造继FinFET之后的核心晶体管结构。目前,三星电子(Samsung)、台积电(Intel)与因特尔(TSMC)已经或者即将在3纳米及以下技术节点采用该器件进行工艺量产。但其被内侧墙隔开的堆叠纳米片沟道会导致非连续源漏选择外延进而产生大量缺陷,引起源漏应变减弱与驱动电流退化,造成较严重的源漏寄生电阻效应,成为其面向高性能电路应用的关键挑战。

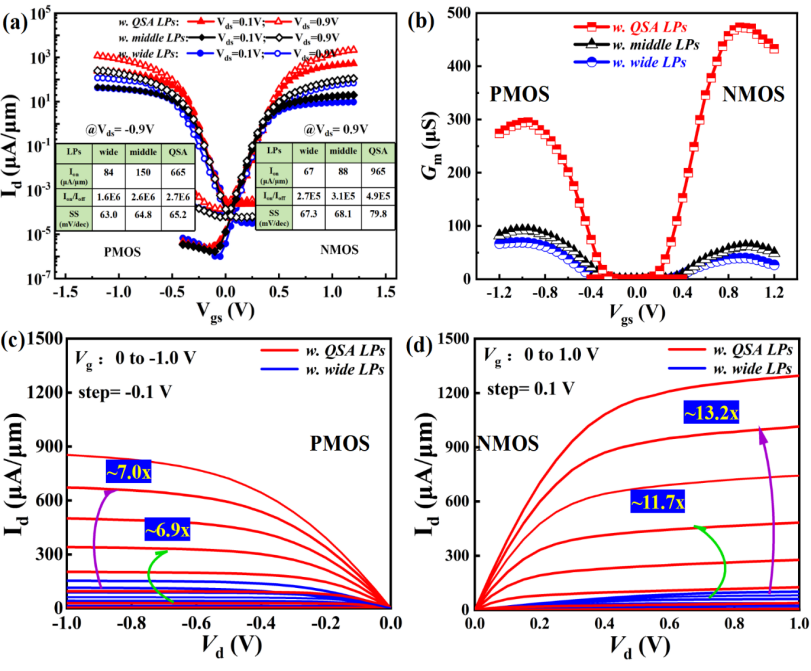

为了突破GAA 器件中严重的源漏选择外延缺陷产生的高寄生电阻和低驱动性能挑战,微电子所集成电路先导工艺研发团队提出了一种与GAA制造工艺兼容的近自对准支撑台(Quasi-Self-Aligned Landing Pads)技术,实现GAA器件中多层堆叠纳米片沟道和单晶 SiGe/Si 超晶格源极/漏极(SD)结构之间的无缺陷连接,同时避免离子注入掺杂引起的源漏缺陷与多晶态。实验结果表明,采用 QSA LPs 技术的 GAA器件的寄生 SD 电阻 (RSD)降低至100Ω,开态电流 (Ion) 值达到 965 μA/μm,达到世界先进水平(见表1),为高性能GAA电路应用提供了一种创新技术方案。

基于本研究成果的论文“High-Performance Gate-All-Around FETs with 100 Ω Parasitic Resistance and 965 μA/μm On-State Current using Quasi-Self-Aligned Landing Pads”(DOI: 10.1109/LED.2024.3505926)近期发表在IEEE Electron Device Letters期刊上,微电子所研究生蒋任婕为第一作者,张青竹研究员和殷华湘研究员为该文共同通讯作者。该项研究得到了中国科学院战略性先导专项(A类)、国家自然科学基金的支持。

论文链接:https://ieeexplore.ieee.org/document/10767246

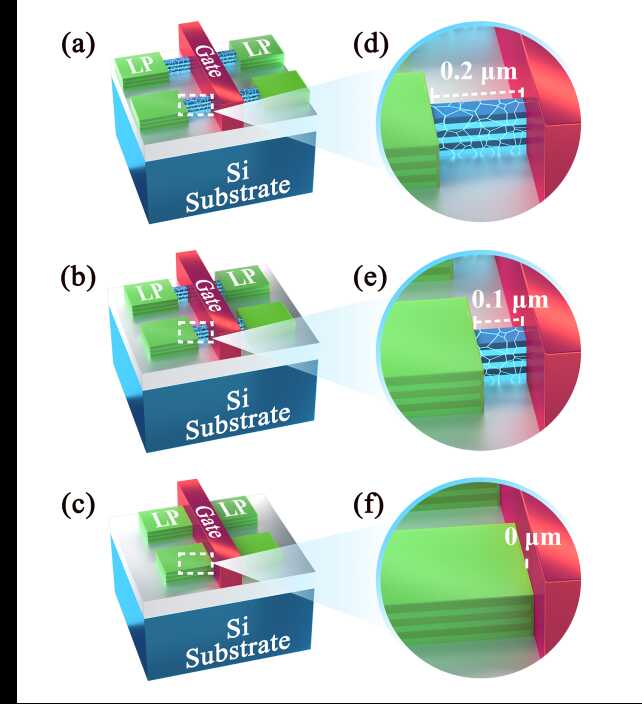

图1 传统GAA和采用近自对准支撑台技术的器件结构

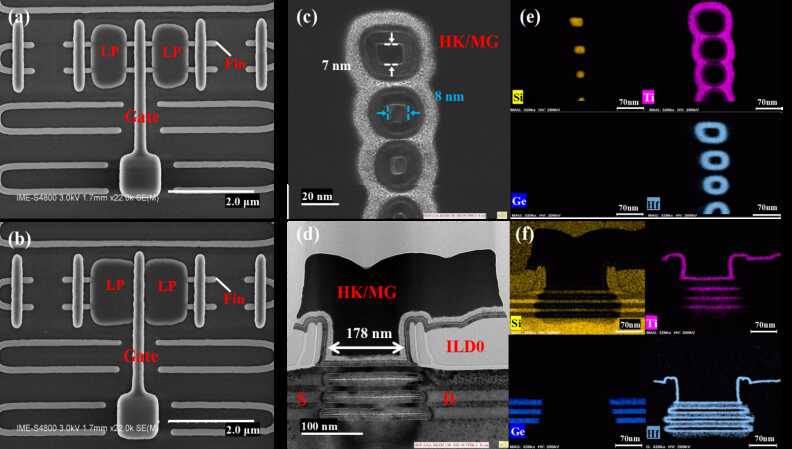

图2 传统GAA和采用近自对准支撑台技术的器件结构与电学特性对比

表1 近年来GAA器件特性参数对比

科研工作