近日,2021 Symposia on VLSI Technology and Circuits国际会议以视频会议的形式召开。其中,中国大陆地区在VLSI Technology共入选6篇论文,其中5篇以微电子所为第一单位,均来自重点实验室刘明院士团队,研究成果覆盖了阻变存储器、先进逻辑器件与技术、器件物理与模型、铁电器件存储器等多项学术前沿领域,这也是重点实验室连续3年在VLSI大会上发表论文。

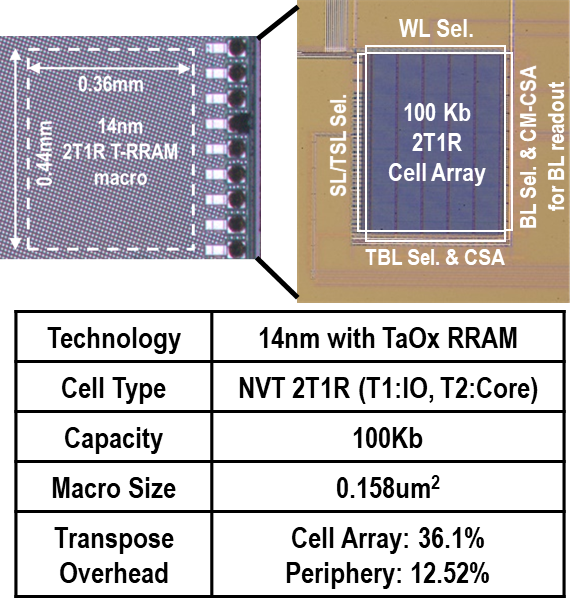

14nm数据转置型RRAM存储器测试芯片研究

数据转置存储器(Transpose Memory)可广泛应用与人工智能处理器以及图像与视频处理器中。虽然其在传统存储器中已经有了成熟的设计方案,但在RRAM等新型存储器中仍然缺乏讨论。研究人员通过协同设计RRAM存储阵列与周边电路,在14纳米 FinFET逻辑工艺平台上实现了100Kbit的嵌入式RRAM存储芯片,在阵列层面,采用两晶体管一阻变单元的新型单元结构。该结构通过第二晶体管栅极实现双方向读出与信号放大、可有效提升读出窗口两个数量级以上。在电路层面,采用双模式的周边译码与快速数据通路稳定技术降低周边电路的面积与功耗开销。这项工作为高能效的转置读取的RRAM存储器设计提供了新思路。该研究成果以题为“A 14nm 100Kb 2T1R Transpose RRAM with >150X resistance ratio enhancement and 27.95% reduction on energy-latency product using low-power near threshold read operation and fast data-line current stabling scheme”入选2021 VLSI Technology。硕士生王琳方为第一作者、叶望为共同一作。

图1.1 测试芯片照片及芯片摘要

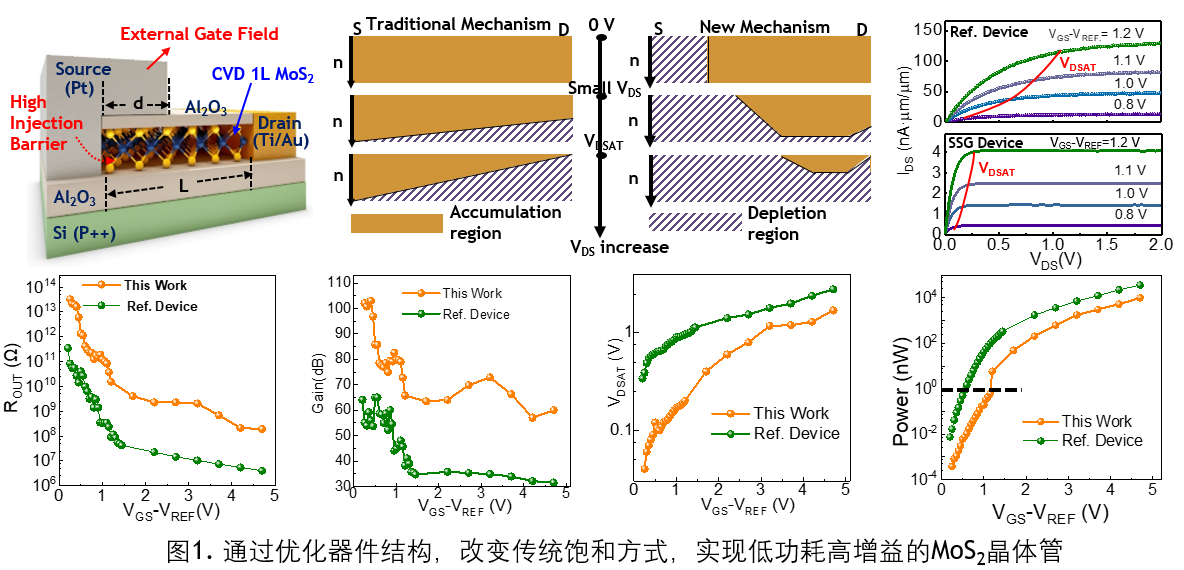

高增益低功耗二硫化钼场效应晶体研究

随着摩尔定律的发展,器件微缩已经开始给硅基晶体管的模拟性能带来潜在问题,其中本征增益作为最重要的模拟指标会随着技术节点的缩小而降低,限制了模拟电路的发展。针对上述问题,研究人员通过对器件结构以及制造工艺的设计与优化,首次将本征电压增益提高到100dB以上,并通过改变传统晶体管的饱和方式实现了超低的饱和电压(VDSAT<0.1V),以及超高的输出电阻,较高的开态电流密度和超低的功耗。相比基准器件,输出电阻在大的和小的VGS-VREF下分别提升了100倍和10-100倍,本征电压增益增加了20-40dB,饱和电压和功耗也有效降低。这项工作推动了MoS2 晶体管本征电压增益和低功耗的进一步提升,对此类器件面向低功耗的模拟电路应用有一定意义。该研究成果以题为“Analog Monolayer MoS2 Transistor with Record-high Intrinsic Gain (>100 dB) and Ultra-low Saturation Voltage (<0.1 V) by Source Engineering”入选2021 VLSI Technology。硕士生刘孟淦为第一作者。

图2.1 通过优化器件结构、改变传统饱和方式、实现低功耗高增益的MoS2晶体管

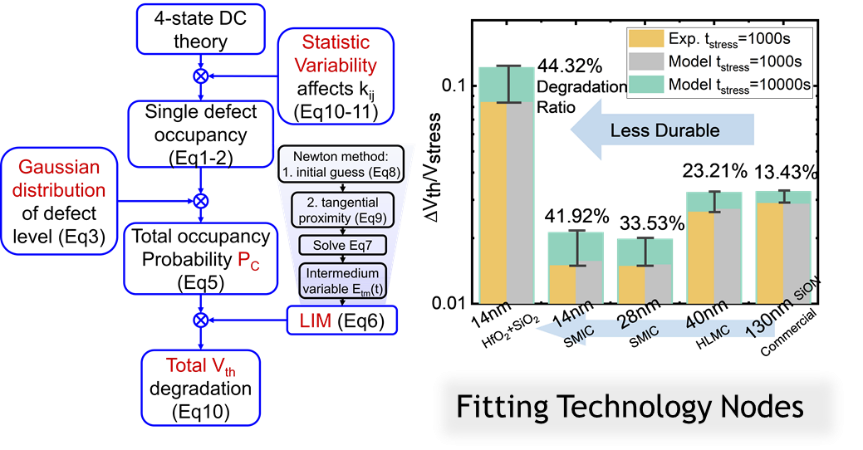

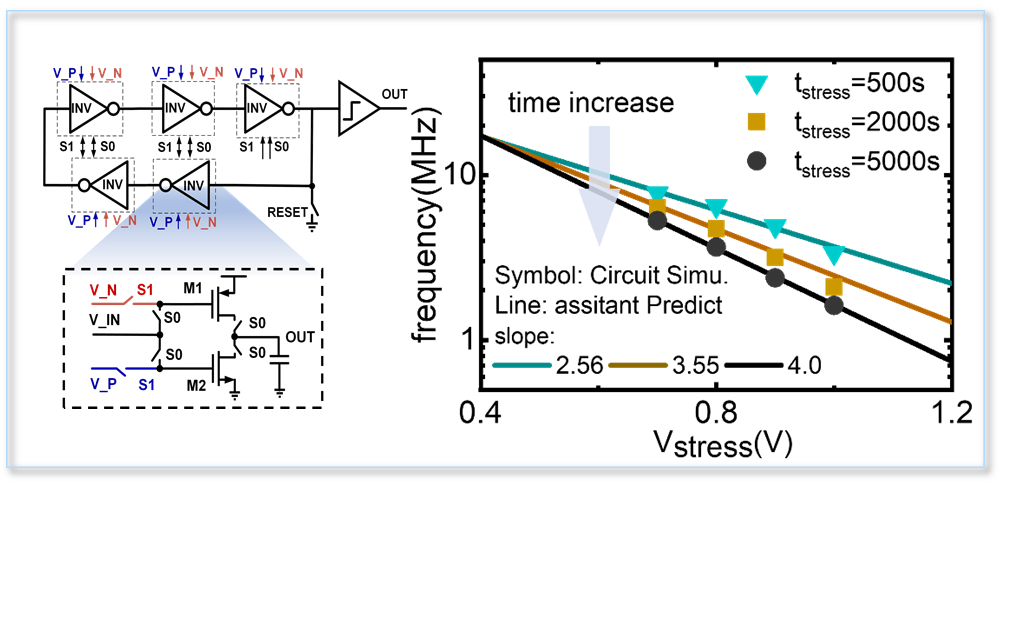

晶体管BTI模型研究

偏置温度不稳定(BTI)效应是集成电路(IC)器件可靠性的关键问题之一,研究人员开发了一个统一的物理和统计紧凑模型,可以预测BTI对不同工艺节点的器件及电路(低至14nm)的影响,包含复杂的应力/恢复模式表征、超长期老化预测和工艺统计变量(TSV)的影响,实现cycle to cycle/device to device的可靠性评估。该模型基于2/4态的缺陷中心(DC)理论,针对缺陷的物理特性(如能级分布、占据概率等)建模。通过TCAD仿真验证和对鳍状场效应晶体管(FinFET)、平面晶体管等实验的校准,成功地嵌入了BSIM-CMG用于器件及电路的动态时间演化和动态电压缩放分析。这种物理的、可变性的和具有耐久性感知的紧凑模型有潜力将VLSI可靠性设计技术协同优化(DTCO)流程提升到下一代技术节点。该研究成果以题为“A Unified Physical BTI Compact Model in Variability-Aware DTCO Flow: Device Characterization and Circuit Evaluation on Reliability of Scaling Technology Nodes”入选2021 VLSI Technology。博士生赵莹为第一作者。

图3.1 基于4-state缺陷中心的BTI紧凑模型,可适用多种工艺节点并给出耐久性分析

图3.2 嵌入了BSIM-CMG用于器件及电路老化性能的动态时间演化和预测分析

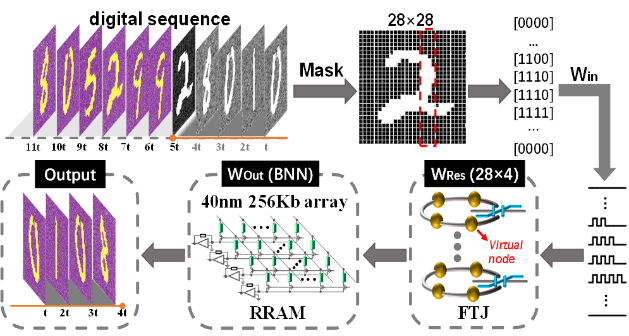

基于超薄FTJ构建储备池计算研究

储备池计算(RC)是循环神经网络的一种简化形式,相比于循环神经网络,可以借助高维度的储备池以低成本、高效率的方式处理时间序列数据。使用硅基器件构建储备池是硬件实现储备池计算的一大难题。针对上述问题,研究人员首次使用超薄(3.5nm)铁电隧穿结(FTJ),利用其瞬态退极化属性作为物理非线性虚拟节点,构建了高能效储备池。通过构造基于FTJ的储备池,并将其与基于RRAM的二值化输出层组合,用于数字序列分类,实现高能效(35pj),高处理速度(500ns)和较高识别准确度(92.3%)。该研究成果以题为“Energy efficient and robust reservoir computing system using ultrathin (3.5 nm) ferroelectric tunneling junctions for temporal data learning”入选2021 VLSI Technology。博士生余杰为第一作者,李熠为共同一作。

图4.1 基于动态FTJ的RC系统原理图

图4.2 RC硬件系统

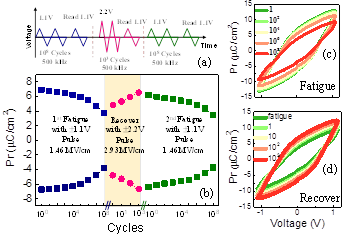

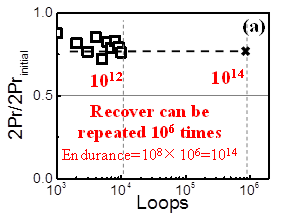

铪基铁电器件研究

高的操作电压以及低的耐久特性阻碍了铪基铁电材料在非挥发性DRAM中的应用。为了解决这个问题,研究人员提出了一种可以提高铪基铁电材料耐久特性的可恢复算法。通过电学表征手段、第一性原理计算以及STEM表征手段系统,团队分析了铪基铁电材料在小电场作用下的失效机理。实验结果表明,铪基铁电材料在小电场下的失效过程同电子脱离陷阱过程有关。在此基础上,团队提出了一种新的可恢复算法,可以使器件的耐久特性得到高于5个数量级的大幅提升。铪基铁电材料的优异性能(1.1V操作电压,非挥发性以及>1014 的耐久特性)为其应用在1z节点非挥发性DRAM上提供了可能。该研究成果以题为“>105 Endurance Improvement of FE-HZO by an Innovative Rejuvenation Method for 1z Node NV-DRAM Applications”入选2021 VLSI Technology。龚天成博士为第一作者。

图5.1可恢复性算法的提出,可以将疲劳后的器件的Pr值恢复

图5.2 器件可以达到1014次方的耐久性,为应用于NV-DRAM提供了可能

背景介绍:

VLSI与ISSCC(国际固态电路会议)、IEDM(国际电子器件会议)并称微电子技术领域的“奥林匹克盛会”,VLSI是超大规模集成电路和半导体器件领域里最顶尖的国际会议之一,是展现IC技术最新成果的重要窗口。

相关链接:https://vlsisymposium.org

综合信息