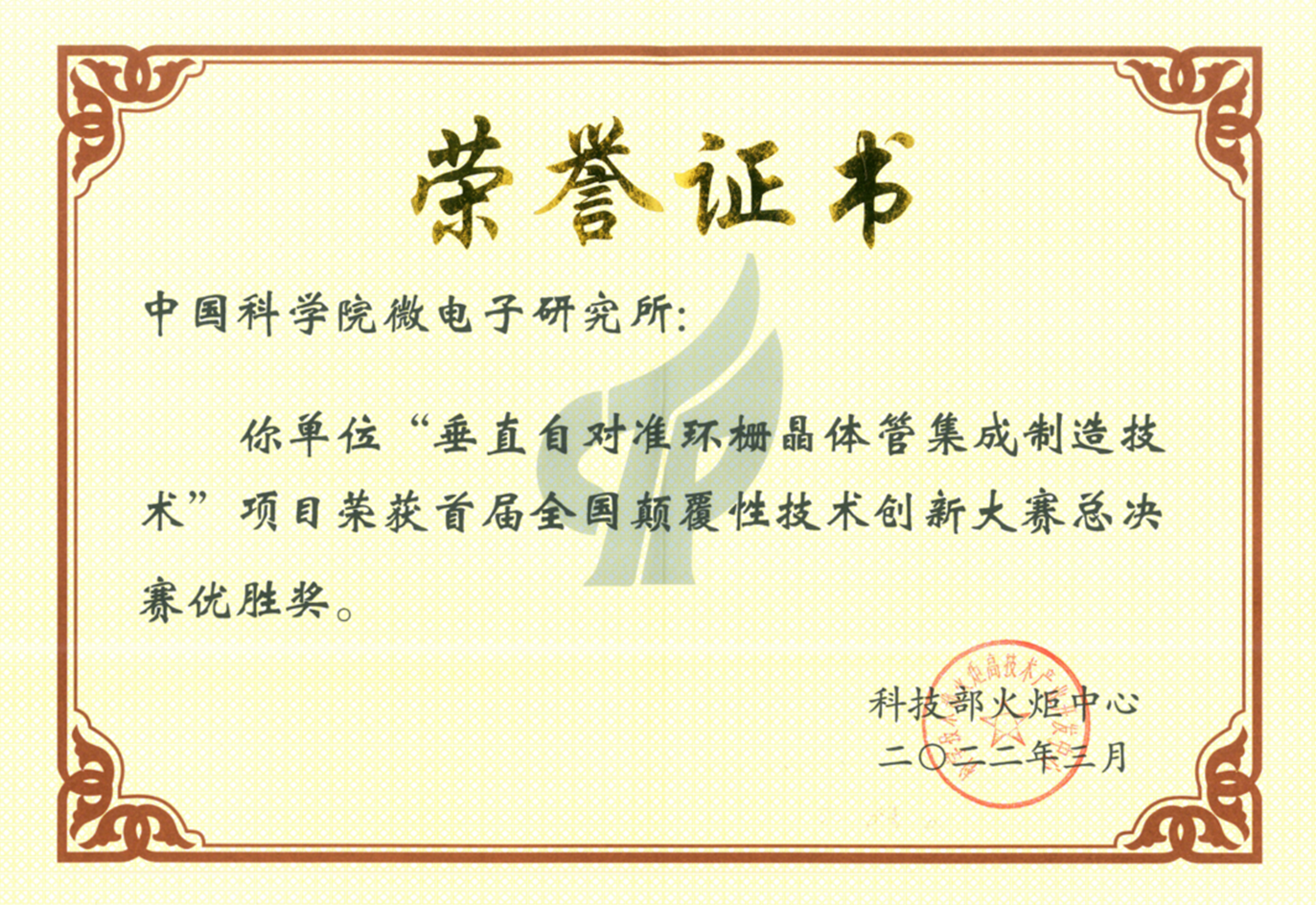

近日,由科技部主办的首届全国颠覆性技术创新大赛落下帷幕,中国科学院微电子研究所集成电路先导工艺研发中心朱慧珑研究员课题组的“垂直自对准环栅晶体管集成制造技术”项目,从全国2724个报名参赛项目中脱颖而出,以领域赛和全国赛两次均全票通过的优异成绩,斩获本次大赛的最高奖项——总决赛优胜奖(共36项)。

垂直纳米环栅晶体管因其在减小标准单元面积、提升性能和改善寄生效应等方面具有天然优势,能满足功耗、性能、面积和成本等设计要求,已成为集成电路2纳米及以下技术代的主要候选器件,但其在器件性能提升和可制造性等方面面临众多挑战。

在专利指导研发和研发面向生产的指导思想下,朱慧珑课题组从2016年起,对垂直晶体管的基础器件和关键工艺开展了系统的专利布局和研发,提出并实现了世界上首个具有自对准栅极的叠层垂直纳米环栅晶体管(Vertical Sandwich Gate-All-Around FETs或VSAFETs),在此基础上又发明并制造出一种可精确控制单晶沟道尺寸的新型垂直纳米环栅晶体管(Vertical C-channel FETs或VCCFETs)。课题组现已申请发明专利120多件,已获授权发明专利50件,含美国授权专利12件;并先后完成了具有自对准栅极的p型/n型MOSFET、闪存器件、1T1C DRAM、TFET、Ge VSAFET和VCCFET等性能优异的垂直器件研发,部分成果发表在IEEE EDL、TED、Nano Letters等本领域顶级期刊上,成为ESI高引用/热点论文和EDL编辑特选(Editors’Picks)论文。研制出的新型垂直晶体管对掺杂分布、沟道尺寸、栅长和栅极位置等极为关键的器件几何参数实现了纳米级精准控制,精度优于现先进光刻和刻蚀技术的水平;主要器件电学性能(开关比、开态电流、SS、DIBL、GIDL)超过目前已报道的同类器件,居世界领先水平。研发出的垂直纳米环栅晶体管制造工艺与主流CMOS工艺兼容,便于3D一体集成,极大地改善了工艺波动,为在量产线进行大规模制造奠定了坚实基础。

综合信息