随着芯片工艺制造的进步,工艺制程逐渐接近物理极限,深度神经网络的发展使得计算量和参数量呈指数上升,阻变存储器应用于大规模神经网络面临多个个挑战:1)由于卷积神经网络权值数量不断增加,使得阻变存储器的面积开销越来越大;2)对于多值大规模阻变存储器阵列,当参与乘累加计算的阻变单元数量很大时,由于阻变单元电导漂移而引起的误差累积更严重;3)三维阻变存储器阵列由于制造工艺难度更大,使得阻变单元与电路协同设计实现困难。

针对上述问题,微电子研究所重点实验室刘明院士团队研发了基于三维阻变存储器存内计算宏芯片。科研人员将多值自选通(Multi-level self-selective,MLSS)三维垂直阻变存储器与抗漂移多位模拟输入权值乘(ADINWM)方案相结合,实现了高密度计算;在抗漂移多位模拟输入权值乘方案基础上提出了电流幅值离散整形(CADS)电路用于增加读出电流的感知容限(SM)用于后续精确的模拟乘法计算,解决了由于三维阻变存储器阵列单元电导波动引起的在传统并行字线输入原位乘累加方案下不可恢复的读出电流失真;采用nA级操作电流的三维垂直阻变存储器阵列降低系统功耗,同时引入具有栅预充电开关跟随器(GPSF)的模拟乘法器与直接小电流模数转换器降低延时。当输入、权重和输出数据分别为8位、9位和22位时,位密度为58.2 bit/μm–2,能效为8.32 TOPS/W。与传统方法相比,提供了更准确的大脑MRI边缘检测和更高的CIFAR-10数据集推理精度。

上述研究成果以“A Computing-in-memory macro with three dimensional resistive random-access memory”为题在电子学领域国际顶级期刊《自然-电子学》(Nature Electronics)上在线发表,实现了中科院微电子所在Nature大类子刊零的突破。微电子所霍强博士为第一作者,北京理工大学杨镒铭为共同第一作者,微电子所张锋研究员和北京理工大学王兴华副教授为共同通讯作者。

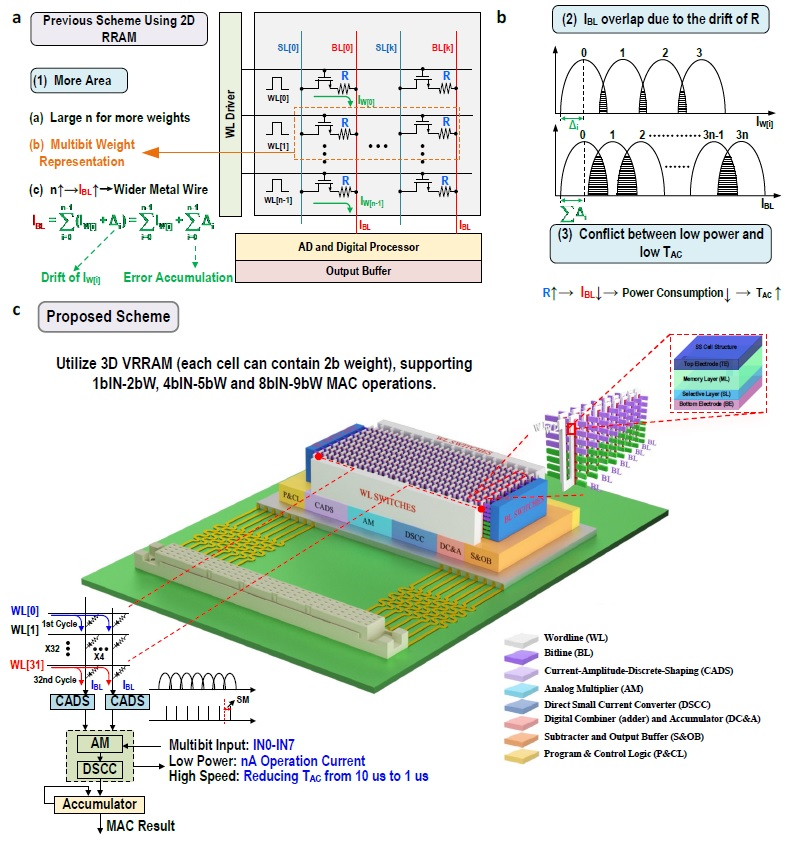

图1. 2D RRAM应用于大型3D CNN的挑战及所提出的三维计算方案。a、更多的权重、多位权重表示和更宽的金属线引入更多设计难题 b、读出电流的挑战是交叠及低功耗和低延迟之间的矛盾。c、基于MLSS 3D VRRAM的高精度非易失存内计算方案。借助CADS电路的ADINWM方案可以有效缓解传统PWIVMM方案引起的电流交叠,提高推理精度。基于集成3D VRRAM芯片的CIM宏的实现阐述了执行CNN边缘计算的完整解决方案。

原文链接:https://www.nature.com/articles/s41928-022-00795-x

综合信息