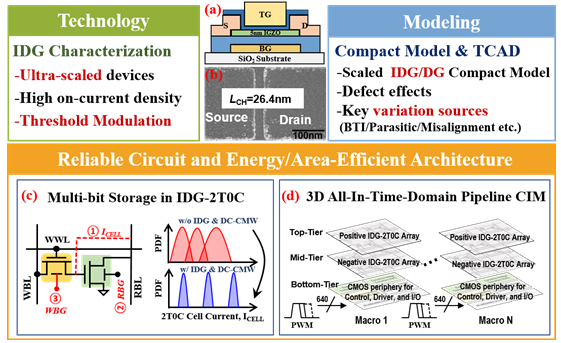

超大规模独立双栅(IDG)InGaZnO-FET具有低漏电、操作灵活和三维集成的特点,有望实现高能效和高密度的存内计算。但其复杂的工作原理、增加的变化源和扩大的寄生效应阻碍了器件建模和电路设计。

针对上述问题,开发了一种可靠性感知的紧凑型模型(RaCM),研究了纳米级 IDG IGZO TFT 的可靠性问题(BTI、多器件阈值电压波动、错位和寄生问题)。通过实验(LCH~26nm)和 TCAD 校准,提出了一种 IDG-2T0C 多比特计算单元,它采用二极管连接写入策略抑制变化,并采用独立栅极增强数据完整性和保留方案。首次使用 28 纳米 Si-CMOS 和 26 纳米 IGZO 器件进行可靠性感知的混合电路仿真,它实现了高达 2766 TOPS/W 的归一化能效 (EF),和现有技术相比性能提高了3倍以上,且在1000s之后,CIFAR-10 推理精度损失小于 2%。

基于该成果的文章“Reliability-Aware Ultra-Scaled IDG-InGaZnO-FET Compact Model to Enable Cross-layer Co-design for Highly Efficient Analog Computing in 2T0C-DRAM”入选2023 IEDM。微电子所博士生徐丽华、陈楷飞、李智为共同第一作者,微电子所窦春萌研究员、杨冠华研究员和汪令飞研究员为共同通讯作者。

(a) 独立双栅非晶IGZO晶体管的原理图和

(b) SEM图

(c) 实现IDG-2T0C多值存储的关键技术

(d) 三维多比特模拟全时域CIM 架构图

综合信息