近日,中科院微电子研究所高频高压中心刘新宇研究员团队与中国科学院苏州纳米所孙钱研究员团队合作,基于前期在高性能n沟道超薄势垒增强型HEMT(或n-FETs)研究中积累的研发基础,结合氮化物特有的极化能带调控引入AlN极化插入层,获得了面密度2.1×1013 cm-2的二维空穴气(2-D Hole Gas,2DHG),为高性能p-FETs乃至GaN基CMOS的研制奠定了材料基础。同时,团队通过引入重掺杂p++-GaN盖帽层初步改善了p-FETs经常存在欧姆接触势垒的问题,并基于团队开发的低损伤p-GaN刻蚀,创新设计出一种阶梯式栅槽刻蚀的增强型GaN基p-FET(图1(a)),克服了由重掺杂p++-GaN层导致的器件击穿降低的不足。

图1.(a)GaN基p-FETs器件结构图;(b)刻蚀与未刻蚀欧姆金属之间p++-GaN的TLM测试结果图;(c)接触区能带图;(d)AFM测得的栅槽截面图

GaN材料具有大禁带宽度(~3.4 eV, Si: ~1.1 eV)、高临界击穿电场(~3.3 MV/cm, Si: ~0.3 MV/cm)、高电子漂移饱和速度(~2.5×107 cm/s, Si: ~1×107 cm/s)及高热导率、高化学稳定性等性能优势,因此非常适用于高频、高功率电力电子及射频器件的制备。目前,基于AlGaN/GaN异质结构的高电子迁移率晶体管(High Electron Mobility Transistors, HEMTs)在手机快充及5G通信领域均已经实现了产业化应用,发挥着不可替代的作用。然而,GaN分立器件的逻辑控制和前级驱动目前大多仍是采用Si基的数字电路,极大的制约了GaN器件高频应用优势的发挥,阻碍了GaN器件在芯片电源管理,以及高温、辐照等极端场景下的应用拓展。互补金属氧化物半导体(Complementary Metal Oxide Semiconductor, CMOS)由于其突出的静态功耗优势,是目前逻辑控制芯片中普遍应用的技术方案,因此基于GaN材料的CMOS技术是推动GaN功率集成电路产业发展至关重要的技术支撑,必将进一步推动GaN功率芯片的智能小型化。

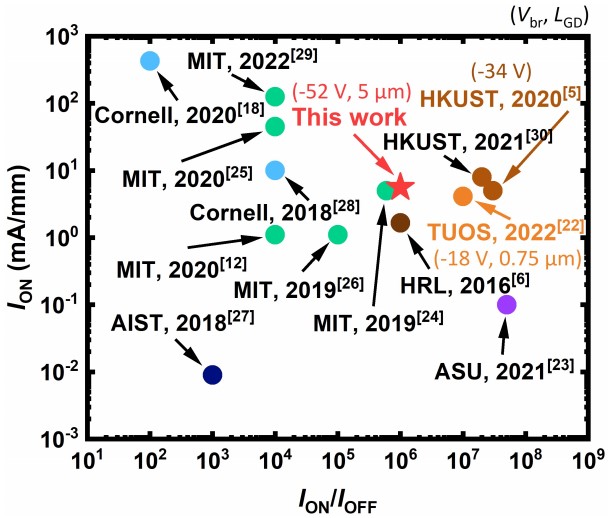

GaN基CMOS技术发展面临的主要瓶颈之一是高性能p沟道场效应晶体管(p-channel Field Effect Transistors, p-FETs)的研制。本研究发现,外延片表面整体生长的Mg受主重掺杂p++-GaN层可以有效降低欧姆接触电阻至15.69 Ω·mm(图1(b)),同时,结合霍尔测试和能带仿真计算结果证明了在p-GaN/AlGaN之间插入的AlN极化增强层可以有效提升二维空穴气面密度至2.1×1013 cm-2(图1(c)),二者对于提升GaN基p-FET的电流能力都有重要的作用。但另一方面,p++-GaN层的引入会使器件的耐压下降,研究团队首先基于TCAD仿真计算确定了器件的击穿主要发生在T型栅靠近漏端的栅帽边缘处,进而提出了阶梯式栅槽刻蚀的技术方案(图1(d)),通过将栅金属与p++-GaN层在空间上进行分离,在实现增强型及低欧姆接触电阻的同时,提高了p-FET的击穿电压。本研究制备的GaN基p-FET具有106的高电流开关比、-5.6 mA/mm的电流密度及-52 V的击穿电压(图2),性能指标均处于国际先进水平(图3)。

图2. GaN基p-FETs的(a)转移特性曲线;(b)输出特性曲线;(c)耐压测试曲线

图3. 本研究GaN基p-FETs的电流密度、电流开关比及击穿电压与国内外同类型器件对比图

相关研究成果将于2022年8月以“An Enhancement-mode GaN p-FET with Improved Breakdown Voltage”为题在线发表于IEEE Electron Device Letters期刊(DOI: 10.1109/LED.2022.3184998);其中博士研究生金昊为论文第一作者,黄森和蒋其梦研究员为共同通讯作者。该工作得到了国家重点研发计划、国家自然科学基金、中国科学院前沿科学重点研究项目以及北京市科委项目等项目的支持。

综合信息