当前,5G/6G、人工智能和高性能计算等应用的快速发展,推动了数据中心交换网络数据传输速率的迅速增长,对高速有线收发机的数据速率、均衡强度、时钟抖动和误码率等性能提出了更高要求。基于ADC-DSP架构的PAM-4调制有线收发机具有均衡强度大、频谱效率高、时钟速度宽松等优势,成为56~224Gb/s中长距有线收发机的主流解决方案。对于长距互连,例如处理器到交换机等应用场景,通常采用重定时收发机补偿信道损耗,重置链路抖动预算,并延长通信距离。相较于传统的有线收发机,重定时收发机面临低抖动同步时钟恢复、高速传输输出抖动恶化、补偿精度有限等挑战,限制了自身性能的进一步提升和推广应用。

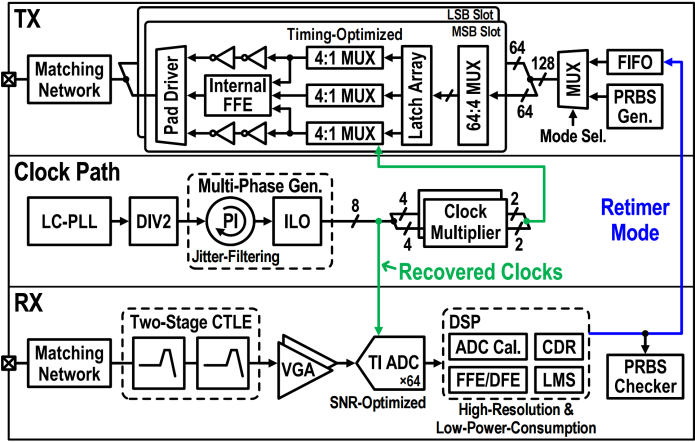

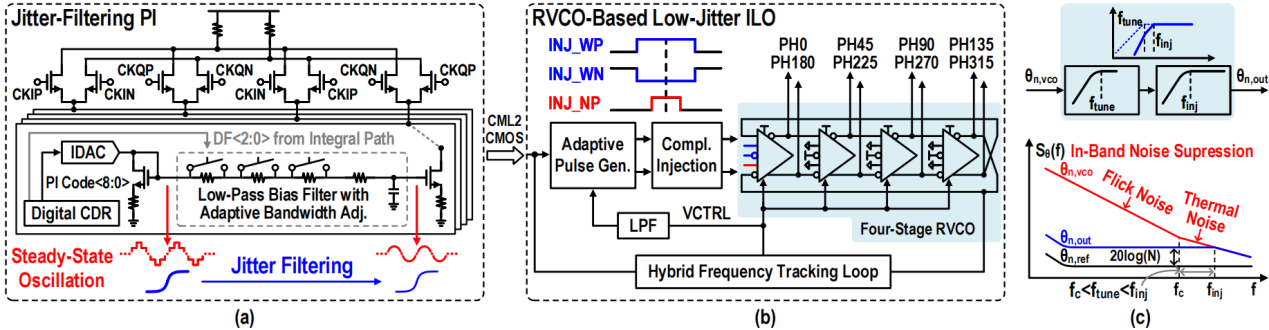

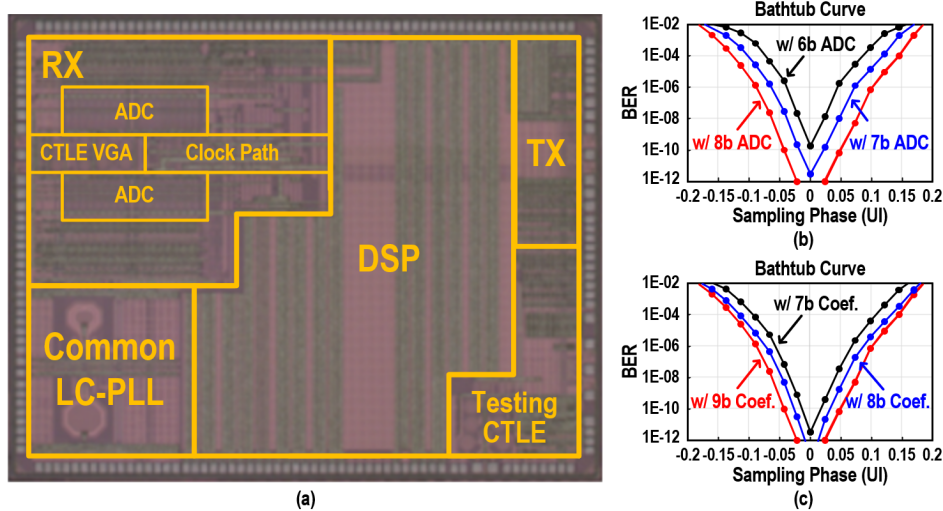

针对上述关键问题,微电子所高频高压中心刘新宇研究员/郑旭强研究员团队研制了一种基于ADC-DSP架构的112-Gb/s PAM-4调制重定时收发机。团队提出了基于注入锁定振荡器的新型抖动滤除时钟方案,在产生低抖动同步恢复时钟的同时降低了时钟路径的功耗;在发射端设计了内部FFE、前馈输出驱动器和时序优化的合路器,实现了输出抖动的降低;在接收端开发了源退化和谐振峰值技术相结合的连续线性时间均衡器以及低功耗、高分辨率数字均衡技术以改善补偿精度,实现了误码率的最小化。该收发机采用28nm CMOS工艺制造,在112Gb/s速率和31dB的信道损耗下实现了1E-12的原始误码率。

研究成果以“A 112-Gb/s PAM-4 Retimer Transceiver with Jitter-Filtering Clocking Scheme and BER Optimization Technique in 28-nm CMOS”为题发表在集成电路设计领域顶级期刊Journal of Solid-State Circuits(JSSC)上,微电子所徐华助理研究员为第一作者,微电子所郑旭强研究员为通讯作者。该项研究得到了国家重点研发计划和国家自然科学基金的支持。

论文链接:https://ieeexplore.ieee.org/document/10955714

图1. 提出的基于ADC-DSP架构的112-Gb/s PAM-4调制重定时收发机

图2. 基于PI-ILO的多相时钟产生(a)抖动滤除相位插值器;(b)基于环形VCO的注入锁定振荡器;

(c)注入锁定振荡器的噪声抑制特性

图3. (a)芯片照片;(b)误码率随ADC分辨率变化图;(c)误码率随数字均衡分辨率变化图

科研工作