近日,微电子所集成电路先导工艺研发中心在源漏接触技术研究方面取得重要进展。

随着集成电路制造技术进入10纳米及以下节点,器件寄生电阻已超过沟道电阻使得器件延迟与功耗显著增大。阻率可降低源漏寄生电阻,对提升器件性能具有重要意义。提高Si表面杂质激活浓度(Ns)以有效增加接触界面的载流子隧穿概率,是减小接触电阻率最重要的方法之一。目前,国际上产业和学术界研发人员主要通过离子注入、高浓度原位掺杂和/或先进激光退火技术来提高Ns,工艺复杂、对工艺设备要求较高且增加了制造成本。

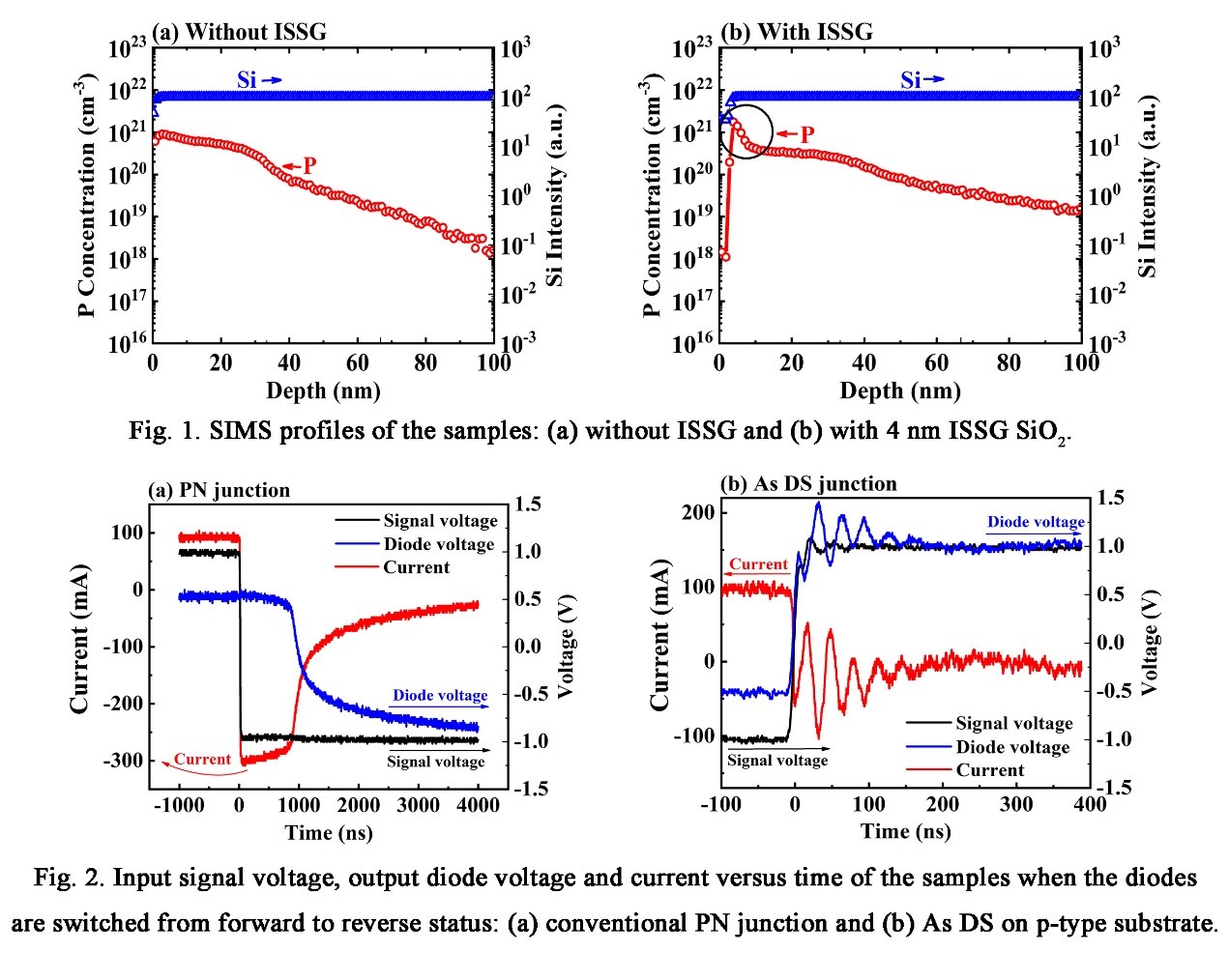

基于以上问题,微电子所先导中心罗军研究员团队创新性利用氧化过程中众所周知的杂质分凝(Dopant Segregation, DS)现象,在源漏接触形成之前采用一步原位水汽氧化工艺(In-situ steam generation, ISSG),提高了半导体衬底表面的Ns。该工艺基于n+-Si衬底,利用Si在氧化过程中,P杂质在Si中的平衡浓度大于在SiO2中的平衡浓度,使得氧化后P杂质分凝于n+-Si表面,从而将Ns提高~1倍、接触电阻率降低了~34.83%(图1)。ISSG氧化工艺简单易行,与现有CMOS集成工艺完全兼容,将此方法应用于提高Ns从而降低源漏寄生电阻具有很高的应用价值,该研究结果也获得7位审稿人一致认可。

基于该研究成果的论文“A Novel Method to Reduce Specific Contact Resistivity of TiSix/n+-Si contacts by Employing An In-situ Steam Generation Oxidation Prior to Ti Silicidation”近期发表在国际微电子器件领域的高水平期刊《IEEE Electron Device Letters》上(DOI: 10.1109/LED.2021.3081701)。微电子所先导中心博士研究生张丹为该文章的第一作者,罗军研究员为该文章的通讯作者。

同时,团队对DS现象降低源漏接触电阻率的机理进行了深入研究,成功解答了长期困扰该领域研发人员的一个难题:当使用与Si衬底掺杂类型相反的杂质形成DS以调整肖特基势垒高度时,会形成silicide/n+-Si/p-Si或者silicide/p+-Si/n-Si结构,此结构究竟是肖特基结还是PN结?团队通过肖特基结与PN结在开关时载流子响应速度的差异,搭建电路进行测试,发现形成DS后的结构仍为肖特基结(图2)。虽然界面处的DS层与衬底掺杂类型相反,但由于其厚度很薄,并没有改变结的性质。

基于该研究成果的论文“NiSi/p+-Si(n+-Si)/n-Si(p-Si) Diodes with Dopant Segregation (DS): PN or Schottky Junctions?”近期也发表在国际微电子器件领域的高水平期刊《IEEE Transactions on Electron Devices》上(DOI: 10.1109/TED.2021.3075199)。微电子所先导中心博士研究生张丹为该文章的第一作者,罗军研究员为该文章的通讯作者。

综合信息